# CD-Player Technologie

SONY

**Technische Information und Schulung**

## CD-Player Technologie

W. Weist H. P. Gerlach

3. Auflage

### Vorwort

Neue Technologien in der Elektronik und Elektrotechnik zwingen die auf diesem Gebiet tätigen Techniker, sich neues theoretisches Basiswissen anzueignen.

Um grundlegende Kenntnisse über Schaltkreise und Funktionsabläufe der Compact-Disc-Abspielgeräte zu vermitteln, wurde ein Seminar erstellt, das den späteren Reparaturanforderungen gerecht wird.

Als Nachschlagewerk für den Lehrgangsteilnehmer wurde die technische Schrift

#### "CD-Player Technologie"

ausgearbeitet.

Ein besonderer Dank gilt den Mitarbeitern E. Littmann, Chr. Krämer und P. Muller, die bei der Erstellung dieser Schrift entscheidend mitgewirkt haben.

W. Weist

Many Shapel H. P. Gerlach

## Inhaltsverzeichnis

|                                                   | Seite |

|---------------------------------------------------|-------|

| Einführung                                        | 1     |

| Übersicht                                         | 1     |

| Grundsätzliches zum CD-Prinzip                    | 1     |

| Abtastung                                         | 5     |

| Herstellungsprozeß der Platte                     | 5     |

| Struktur der CD                                   | 7     |

| Die Pits                                          | 8     |

| Die konstante lineare Abtastgeschwindigkeit       | 9     |

| Die Transparenzschicht                            | 10    |

| Das Auslesen der Pits                             | 11    |

| Optisches Abtastsystem                            | 13    |

| Das Lichtspektrum                                 | 13    |

| Die Injektions-Laserdiode                         | 14    |

| Warum wird zum Auslesen der CD-Information        |       |

| ein Laser benötigt ?                              | 15    |

| APC-Schaltung zur Steuerung der Laserdiode        | 16    |

| Das Strahlbeugungselement                         | 19    |

| Das Polarisationsprisma                           | 19    |

| Platte                                            | 22    |

| Sammellinseneinheit                               | 23    |

| Zylindrische Linse                                | 23    |

| Fokusdetektor                                     | 24    |

| Fracking-Detektor                                 | 26    |

| 2-Achsen-Element                                  | 27    |

| Der Weg des Laserlichts durch das optische System | 28    |

#### INHALTSVERZEICHNIS (Fortsetzung)

|                                                             | Seite |

|-------------------------------------------------------------|-------|

| CD-Aufnahmeverfahren                                        | 30    |

| Theorie der PCM-Technik                                     | 31    |

| Fehlerkorrektur                                             | 41    |

| CIRC-Verschlüsselung                                        | 44    |

| Das Kontrollsignal, der Steuersignalblock                   | 46    |

| Kanal Q, der CRC-Code                                       | 47    |

| Betriebsart ADR-001 für Kanal Q                             | 48    |

| Die EFM                                                     | 50    |

| Minimale und maximale Pitlänge                              | 55    |

| Endgültige Frame-Struktur auf der CD                        | 56    |

| Datenverarbeitung                                           | ,     |

| HF-Offset-Verstärker                                        | 57    |

| Impulsformer-Schaltung                                      | 58    |

| Wiedergabe-Clockfrequenz                                    | 59    |

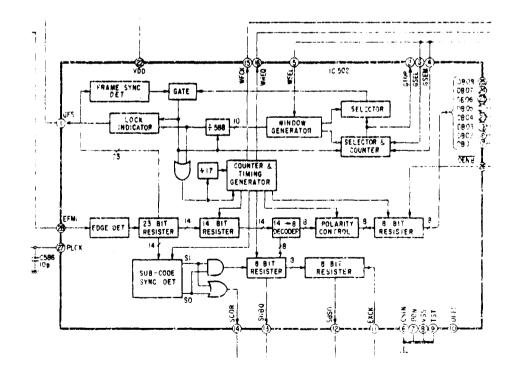

| Digitale Datenverarbeitung mit den LSI-IC's                 | 64    |

| CX-7933                                                     | 64    |

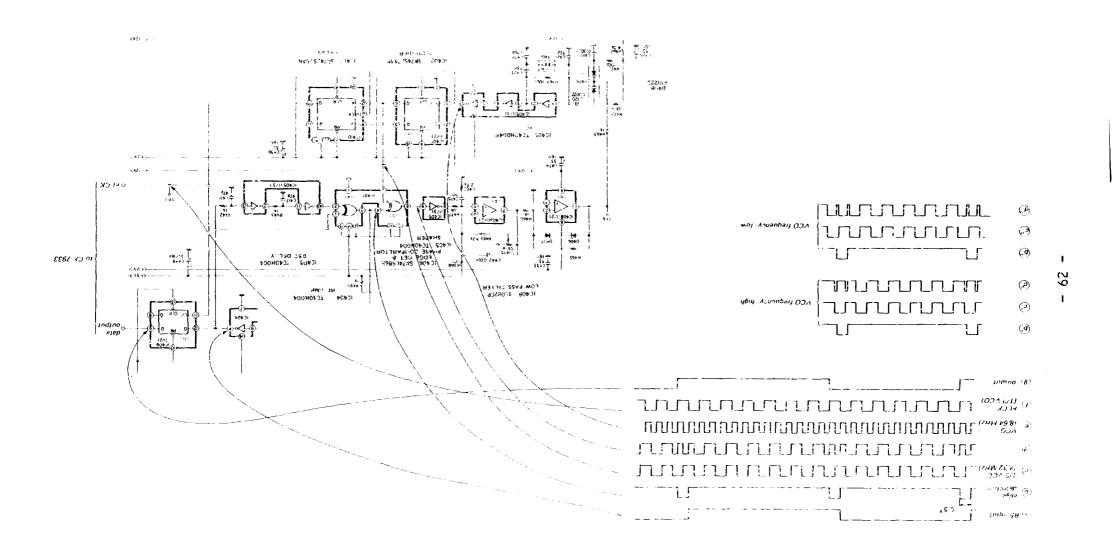

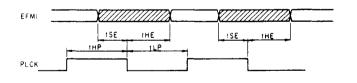

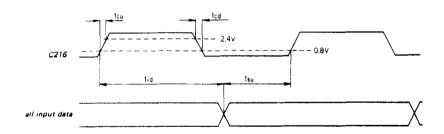

| Zeitlicher Zusammenhang der EFMI-Daten und der PB-Clock     | 67    |

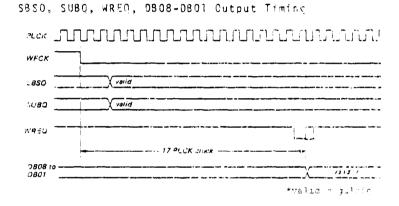

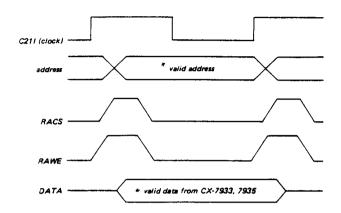

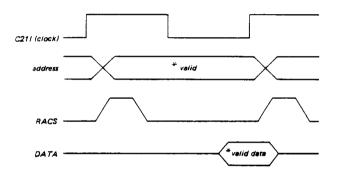

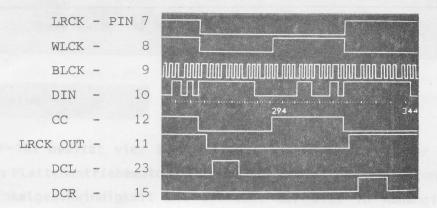

| Timingdiagramme                                             | 68    |

| CX-7934                                                     | 71    |

| Masterclock, De-Interleave, RAM-Adreßgenerator              | 74    |

| Interpolation                                               | 77    |

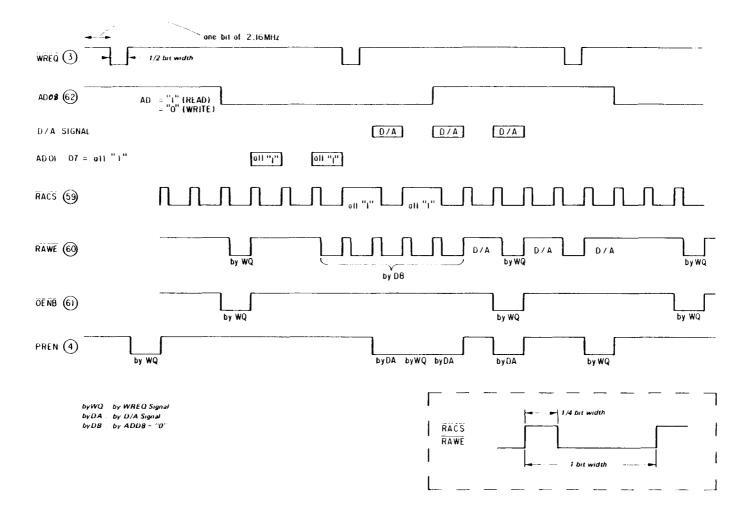

| Interface zum D/A-Wandler, Muting und Abschwächer-Eingänge, |       |

| RFCK und WFCK                                               | 79    |

| cx-7935                                                     | 80    |

| C <sub>1</sub> -Decoder                                     | 82    |

| C <sub>2</sub> -Decoder                                     | 83    |

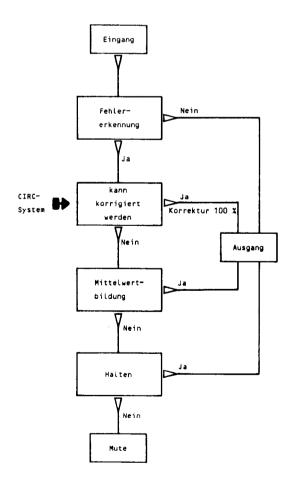

| Fehlerkorrektur                                             | 84    |

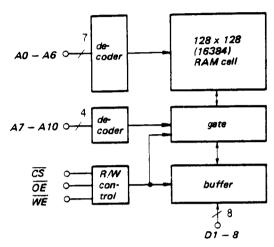

| RAM (MSM-5128)                                              | 85    |

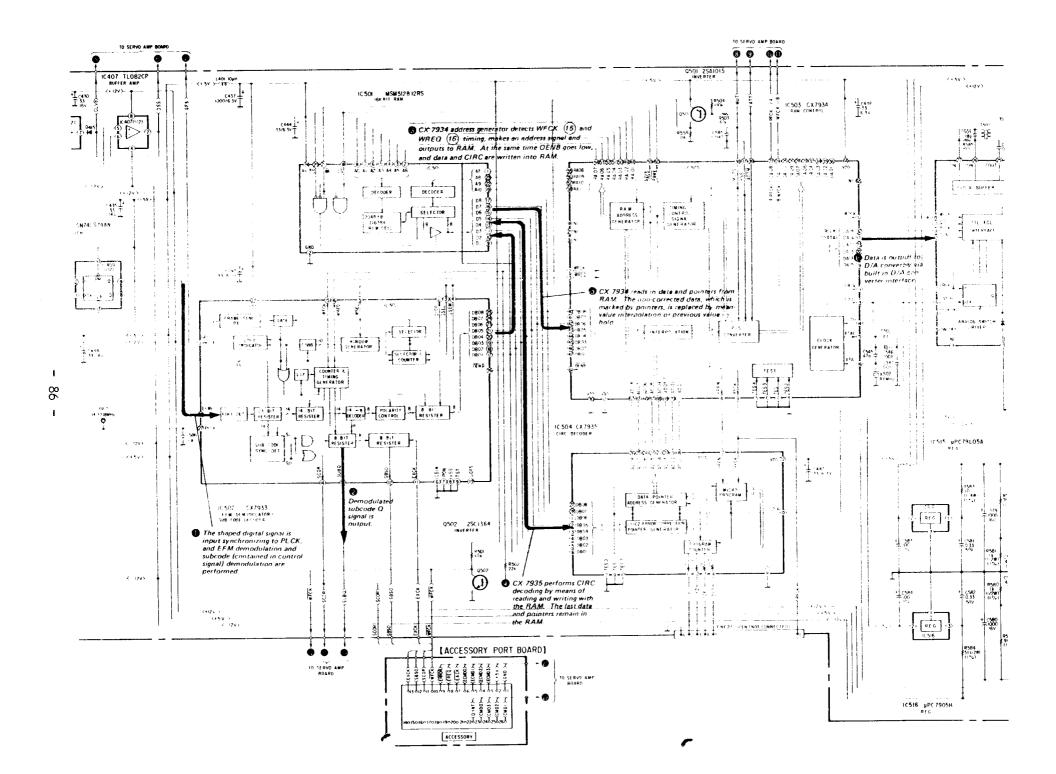

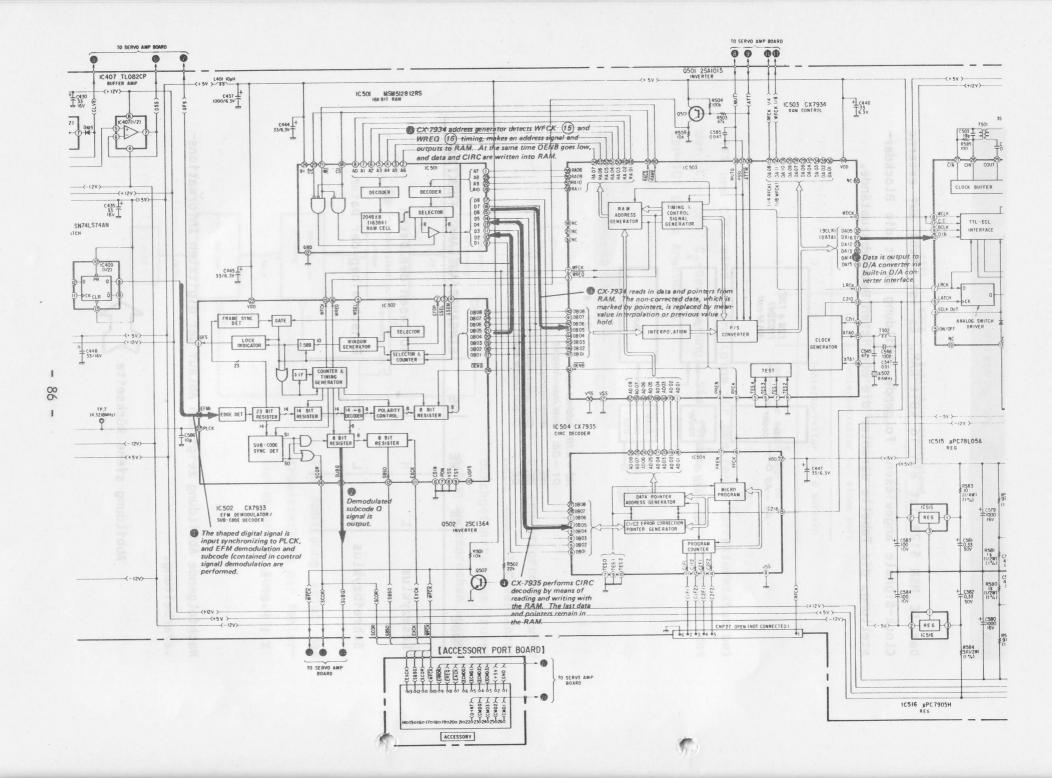

| Arbeitsschema der Datenverarbeitung                         | 86    |

| D/A-Wandler                                                 | 87    |

| Tiefpaß und Deemphasis                                      | 89    |

#### INHALTSVERZEICHNIS (Fortsetzung)

|                                                     | Seite |

|-----------------------------------------------------|-------|

| Servosysteme                                        | 91    |

| Regelkreise                                         | 91    |

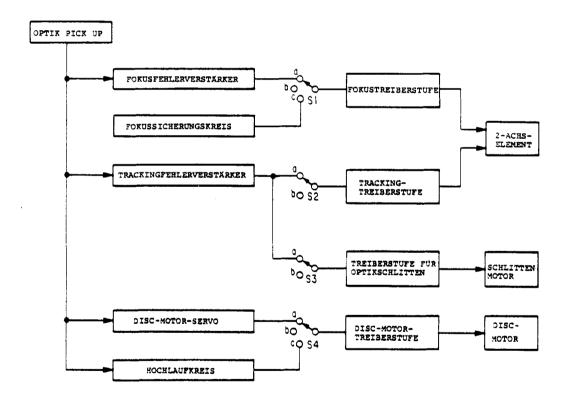

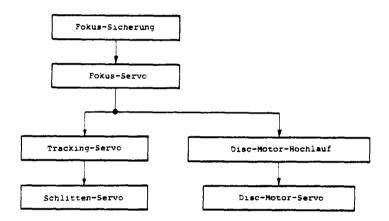

| Ablaufschema der Servofunktionen                    | 92    |

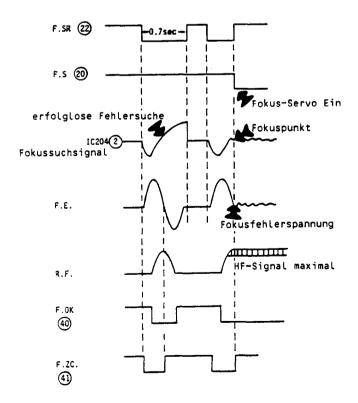

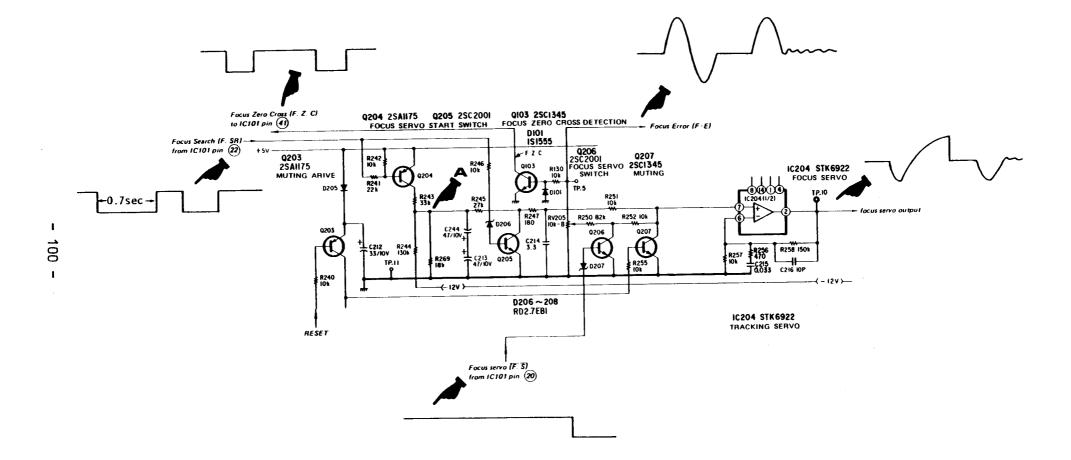

| Fokus-Servokreis                                    | 92    |

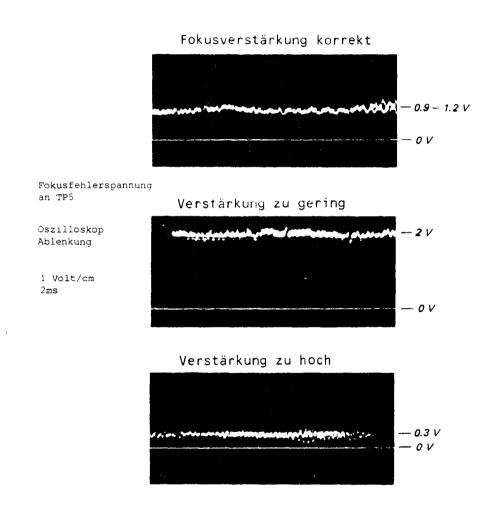

| Fokusfehlerverstärker                               | 92    |

| Fokusservo                                          | 94    |

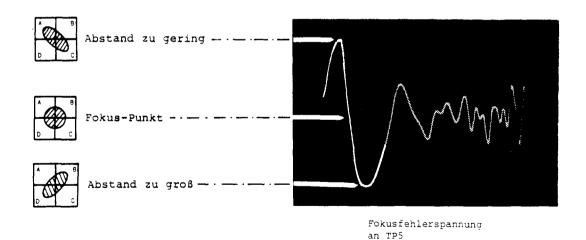

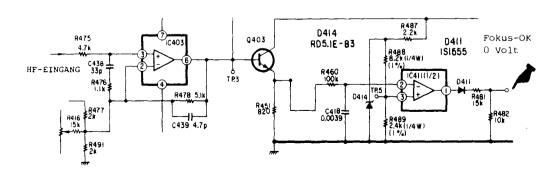

| Detektor für Fokus-OK/Fokus-Nulldurchgang           | 95    |

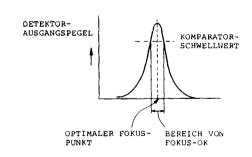

| Fokus-0K                                            | 96    |

| Detektor für Fokus-Nulldurchgang (Focus Zero Cross) | 97    |

| Fokussuche                                          | 98    |

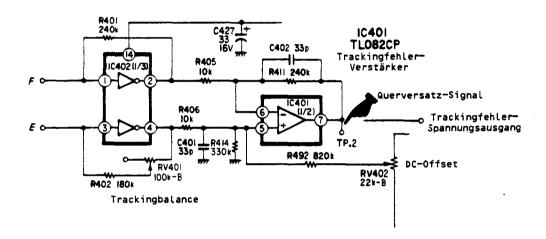

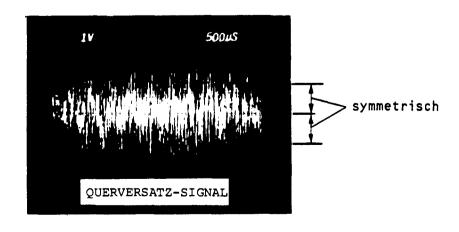

| Tracking-Servokreis                                 | 101   |

| Tracking-Fehlerverstärker                           | 101   |

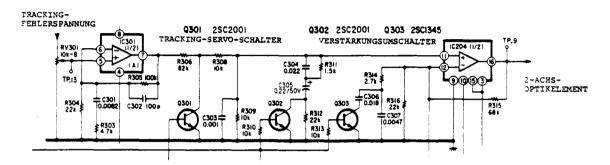

| Tracking-Servo                                      | 102   |

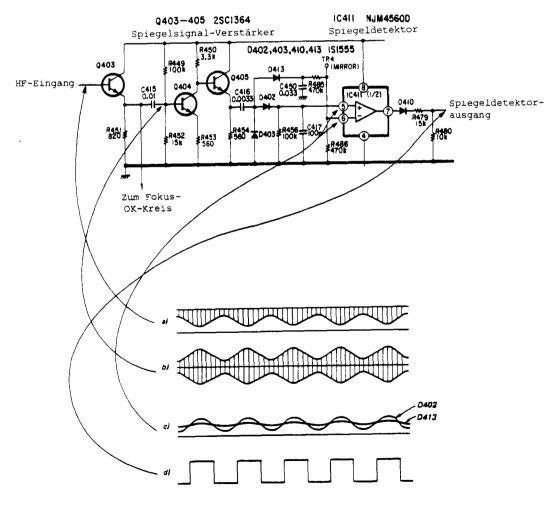

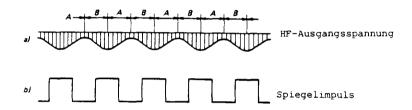

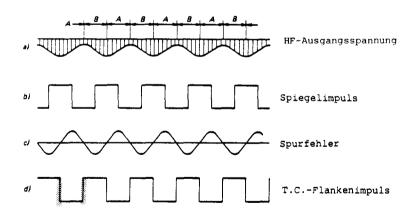

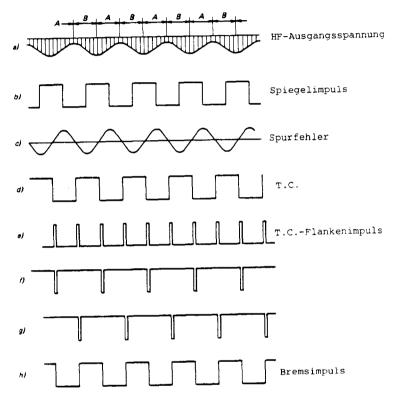

| Spiegeldetektor                                     | 103   |

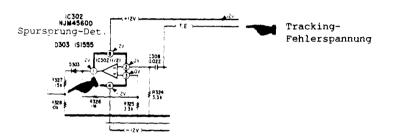

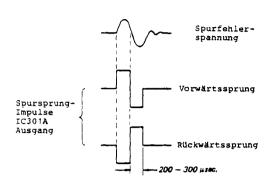

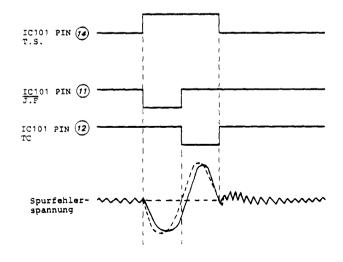

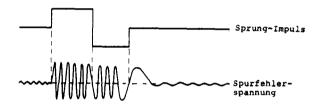

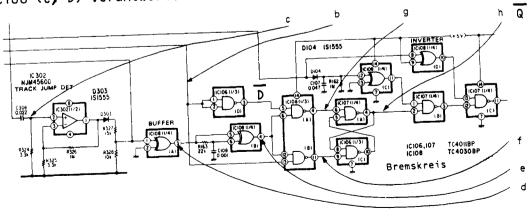

| Spursprung-Detektor                                 | 106   |

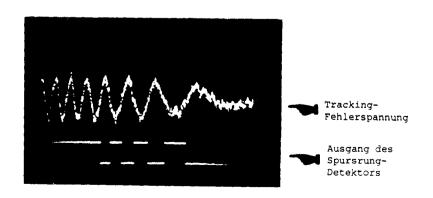

| Spurensprung                                        | 107   |

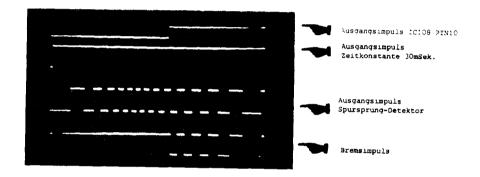

| 1er Spurensprung                                    | 108   |

| 10er Spurensprung                                   | 109   |

| 100er Spurensprung                                  | 110   |

| Bremskreis                                          | 111   |

| Servokreis des Optik-Nachführmotors (sled motor)    | 116   |

| Rückführung des Optikschlittens in Start-Position   | 119   |

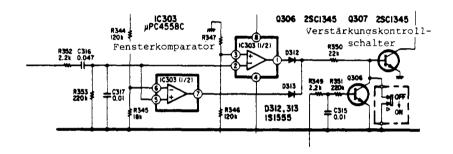

| Fensterkomparator                                   | 120   |

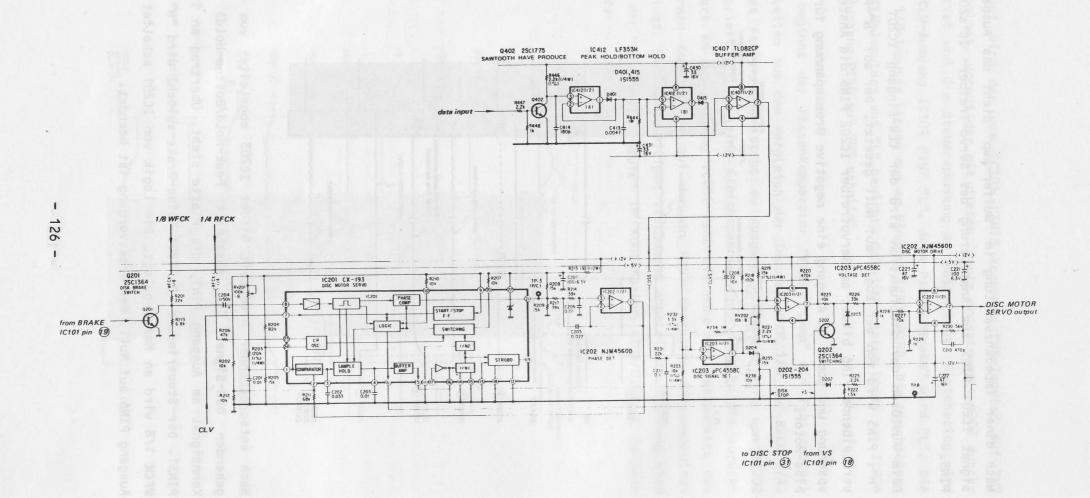

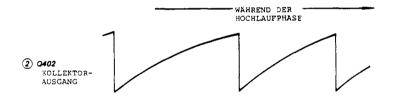

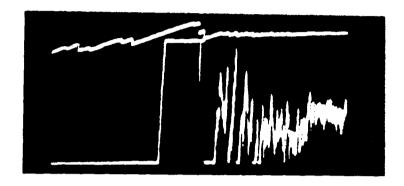

| Disc-Motor-Servo                                    | 122   |

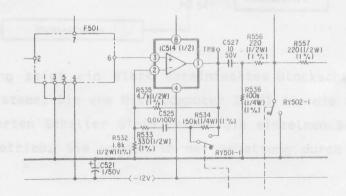

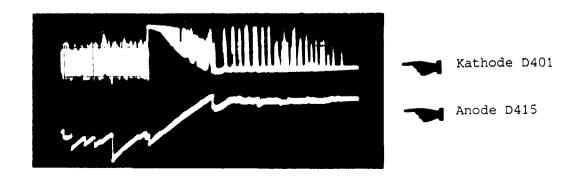

| Peak-Hold/Bottom-Hold                               | 127   |

| Peak-Hold                                           | 127   |

| Bottom-Hold                                         | 128   |

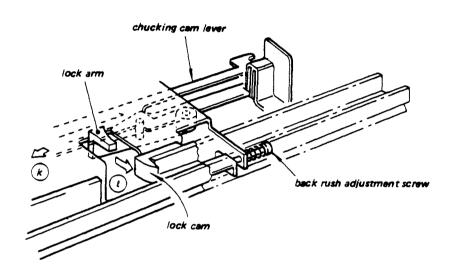

| Laden des Gerätes                                   | 130   |

| Stabilisierungsmechanismus                          | 133   |

| Fixieren der Plattenlade                            | 134   |

| Srklärungen                                         | 135   |

## Einführung

#### ÜBERSICHT

Im Juni 1980 wurde als gemeinsame Entwicklung von SONY und Philips das Compact-Disc-System der öffentlichkeit vorgestellt.

Das CD-System arbeitet mit einem berühungsfreien Abtastsystem. Die Abtastung erfolgt mit einem Halbleiterlaser.

Gegenüber anderen Systemen mit mechanischer Abtastung können hier bei der Abtastung keinerlei mechanische Verschleißerscheinungen an der Platte oder am Abtaster auftreten.

Auch bei diesem System wird die PCM-Technik zur Signalübertragung verwendet, abrilich wie es beim PCM-F1-Prozessor geschieht. Neuartig ist das System der Laserabtastung.

#### Grundsätzliches zum CD-Prinzip

#### Wie wird bei der CD-Platte die Musikinformation gespeichert?

Auf der nur 12 cm durchmessenden CD ist die Information digital gespeichert. Die 1/0-Impulse des PCM-Signals werden als mikroskopisch kleine Vertiefungen ("Pits" genannt) in einer von innen nach außen verlaufenden Spirale in die Platte geprägt, wobei die log. "O" von einer Vertiefung dargestellt wird. Nach der Pressung wird die "Informationsfläche" verspiegelt. Um diese Metallschicht vor mechanischer Beschädigung zu schützen, wird sie mit einer Lackschicht überzogen. Unter der Informationsebene liegt die transparente Trägerschicht mit einem Brechungsindex von 1,46.

#### Wie wird die Information der Platte abgetastet?

Das Auslesen der Information erfolgt mit einem Laser-Lichtstrahl, der von einem Halbleiterlaser erzeugt wird. Der Lichtstrahl liest die Information während des Abtastvorgangs von unten durch die transparente Trägerschicht hindurch.

An den Stellen, an denen keine Vertiefungen eingeprägt sind, wird der Laserstrahl voll reflektiert. An den Prägungen hingegen wird der Lichtstrahl (durch Phasenauslöschung-Interferenz) so stark reduziert, daß fast kein Licht reflektiert wird.

Die Informationen auf der Platte werden praktisch umgesetzt ; Lichtreflektionen.

#### Welche Drehzahl hat diese Schallplatte?

Die Drehzahl der Platte ändert sich während des Abspielens kontinuierlich. Was sind hierfür die Gründe?

Bekannterweise muß man einem Mikroprozessor einen annähernd gleichen Datenstrom anbieten. Würde man nun die Drehzahl wie bei einer herkömmlichen Schallplatte über die gesamte Spielzeit konstant halten, so entstünde, abhängig vom jeweiligen Abtastpunkt (innen oder außen), eine unterschiedlich große Datenzahl, die dem Prozessor angeboten würde.

Das widerspricht jedoch der Forderung, daß dem Prozessor ein konstanter Datenfluß übermittelt werden muß. Daher wird die Drehzahl entsprechend der Forderung nach einer konstanten Bitrate von 4,3 Mio. Bits/sec. nachgeregelt. Die Drehzahl beträgt im Platteninnern ca. 500 U/min. und verringert sich zum Plattenäußeren hir bis auf 200 U/min. Da alle abgetasteten Daten zuerst in einer Speicher eingelesen und dann mittels einer quarzgenauen Taktfrequenz ausgelesen werden, haben Drehzahländerungen der Platte keinen Einfluß auf das Gleichlaufverhalten (Wow und Flutter).

Daher gilt:

Gleichlaufschwankung nicht meßbar!

#### Was ist auf der Platte gespeichert?

Außer der Audioinformation können auf der CD noch weitere Infos, z.B. über die Anzahl der Titel, den Komponisten, den Interpreten oder die Spieldauer gespeichert werden.

Auch Synchronisations- und Fehlerkorrekturdaten, die wichtig für die Funktion des CD-Players sind, werden in die Platte geprägt.

#### Welche Vorteile bietet nun das neue CD-System?

Herkömmliche analoge Tonaufzeichnungen auf Schallplatte sind mit unüberhörbaren Nachteilen behaftet: Die Schwachstellen liegen bei den Übertragungs- und Speichermedien.

Bei der Schallplatte stört vor allem das "Rillengeräusch"; es äußert sich bekannterweise in Rumpel- und Knackgeräuschen. U.a. resultiert hieraus, daß bei herkömmlichen Schallplatten die reproduzierbare Dynamik wesentlich unter der des Originals liegt. Man könnte auch sagen, daß das reine Musiksignal mit den Störsignalen behaftet ist, was eine naturgetreue Musikwiedergabe praktisch unmöglich macht. Aufgrund der bei der CD angewandten PCM-Technik treten alle somit üblichen Rumpel- und Knackgeräusche nicht in Erscheinung.

Alle von der PCM-Aufzeichnung (PCM-F1) her bekannten Vorteile gelten auch für das CD-System:

- 1) Sehr großer Dynamikbereich von mehr als 90 dB

- 2) Großer linearer Übertragungsbereich von 5 20.000 Hz ±0,50 dB

- 3) Klirrfaktorwerte von 0,004% (1 kHz), die mit keiner analogen Aufzeichnungsmethode erreichbar sind

- 4) Kanaltrennung von > 90 dB (im Vergleich hierzu: die Kanaltrennung bei der Wiedergabe einer analogen Schallplatte betragt weniger als 40 dB)

- 5) Nicht meßbare Gleichlaufschwankungen

Neben den für uns wichtigsten Vorzügen in der Tonqualität eigest sich aus dem möglichen datenmäßigen Aufbau der gespeichenten Information in Verbindung mit der prozessorgesteuerten Systemkontrolle des CD-Spielers, ein sehr hoher Bedienungskomfort.

Die nachfolgende Tabelle zeigt eine direkte Gegenüberstellung der wichtigsten Merkmale von CD und der herkömmlichen analogen Schallplatte.

| TECHNISCHE MERKMALE DER CD-TECHNIK IM VERGLEICH ZU HERKOMMLICHEN ANALOG-SCHALLPLATTEN |                         |                                    |  |

|---------------------------------------------------------------------------------------|-------------------------|------------------------------------|--|

|                                                                                       | Daten der Compact-Disc  | Herkömmliche Analog-Schallplatte ( |  |

| Durchmesser                                                                           | 12 cm                   | 30 cm                              |  |

| Plattendicke                                                                          | 1,2 mm                  |                                    |  |

| Rotationsgeschwindigkeit                                                              | 500-200 Upm variabel    | 33 1/3 Upm konstant (LP)           |  |

|                                                                                       | (1,2 m/s konstant       | (=50cm/s außen und 20cm/s innen    |  |

|                                                                                       | oder 1,4 m/s konstant)  |                                    |  |

| Frequenzbereich                                                                       | 5-20.000 Hz + 0,5 dB    | 30-20.000 Hz                       |  |

| Signalrauschabstand                                                                   | ,<br>größer 90 dB       | 55 - 60 dB                         |  |

|                                                                                       | (theoretisch 96 dB)     |                                    |  |

| Dynamikbereich                                                                        | größer 90 dB            | bis ca. 60 dB                      |  |

|                                                                                       | (theoretisch 96 dB)     |                                    |  |

| Kanaltrennung                                                                         | größer 90 dB            | 25 - 35 de                         |  |

| Verzerrungen                                                                          | kleiner 0,004%          | 0,2%                               |  |

| Gleichlaufschwankungen                                                                | nicht meßbar            | ca. 0,03%                          |  |

| Spurabstand                                                                           | 1,6 ,um                 | variabel                           |  |

| Abtastung                                                                             | berührungslos durch La- | mechanisch durch Tonabnehmersyster |  |

|                                                                                       | serstrahl von innen     | von außen nach innen               |  |

|                                                                                       | nach außen              |                                    |  |

| Anzahl der Kanäle                                                                     | 2 (4)                   | 1 oder 2                           |  |

| Spielzeit                                                                             | einseitig bespielt      | beide Seiten zusammen da.45 ***.   |  |

|                                                                                       | ca. 60 Min. ununterbro- |                                    |  |

|                                                                                       | chen bei 2-Kanalauf-    |                                    |  |

|                                                                                       | zeichnung               |                                    |  |

## Abtastung

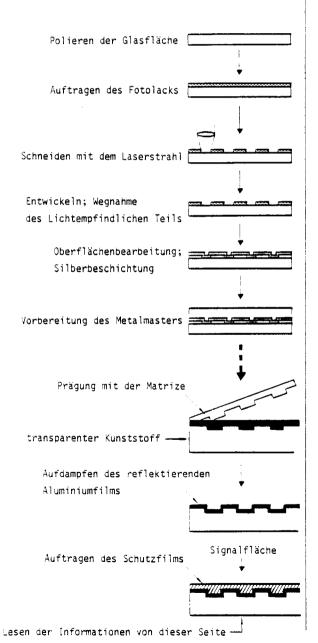

Beginnen wir mit einer schematisierten Darstellung des Herstellungsprozesses der Platte.

### COMPACT DISC (CD) HERSTELLUNG DER SCHALLPLATE

Als erstes wird eine Glasplatte als Aufzeichnungsträger mit einer dünnen Photo-Resist-Schicht überzogen.

Ein mit der digitalen Information modulierter Laserstrahl "schneidet" die Information in die Photoschicht, so daß nach dem Entwicklungsprozess nur die unbelichteten Stellen stehenbleiben. Das Master enthält nach diesem Vorgang die digitale Information in Form von "Pits" sogenannten (Vertiefungen), die spiralförmig angeordnet sind.

Auf galvanischem Wege wird nun eine genaue Negativ-Kopie herge-stellt, die später als Preßmatrize dient.

Es folgt nun eine Oberflächenverarbeitung und das Aufbringen einer Silberschicht. Mit dieser Negativ-Kopie könnte schon eine Hersteltlung einer CD erfolgen.

Um aber die einzige vorhandene Matrize zu schonen, wird hiervon noch einmal eine (oder auch mehrere) Zwischen-Kopie erstellt, die, da sie ein Positiv ist, jedoch nicht als Matrize zu verwenden ist. Diese Zwischenkopie wird auch als "Mutter" bezeichnet. Von dieser Mutter wird dann erst auf galvanischem Wege eine Preßmatrize erstellt (jetzt wieder ein Negativ), womit dann die CD's gepreßt werden. Während dieser ganzen Vorgänge erfolgt keine meßbare Veränderung der Informationsstruktur. Diese Zwischenkopie wird auch als "Mutter" bezeichnet.

Aus dieser Beschreibung läßt sich nun auch ableiten, daß die Pits als Informationsträger auf der Platte ursprünglich Vertiefungen sind.

1. Positiv - Master = Pits (Vertiefungen)

2. Negativ - Kopie = bumps (Erhöhungen)

3. Zwischen - Kopie (Positiv) = Pits (Vertiefungen)

4. Preßmatrize (Negativ) = bumps (Erhöhungen)

5. CD = Labelseite = Pits (Vertiefungen)

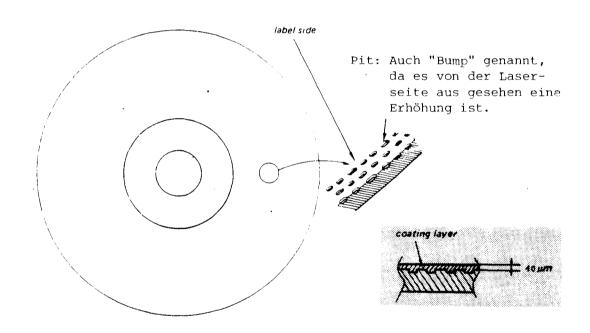

Die Herstellung der CD erfolgt in einem Spritz-Fress-Verfahren, als Material wird Polycarbonat benutzt. Die Oberfläche der Informationsebene der gepreßten CD wird nun verspiegelt, die Spiegelfläche ist hauchdünn,ihre Dicke beträgt nur einige 100 Å\*, Um eine Beschädigung zu vermeiden, wird hierüber eine ca. 5-10 jum starke Schutzschicht aufgetragen.

Diese Schutzschicht wird auch als Labelseite bezeichnet, da hierauf später das Label aufgedruckt wird. Die Auslesung der Information erfolgt mittels Laserstrahl durch die unterhalb der Informationsebene liegende, ca. 1,2 mm dicke Transparentschicht.

$$*\Re = \text{Angströmeinheit}$$

, 1  $\Re = 10^{-4}$  <sub>/um</sub>

Die Pits der Informationsebene erscheinen, da der Laser die Abtastung von unten durch die Transparentschicht vornimmt, von der Optik aus gesehen als Erhöhungen (bumps)!

Der letzte Schritt der eigentlichen Plattenherstellung ist das Stanzen eines zentrischen Mittellochs mit 15 mm Durchmesser.

Bei der Fertigung muß auf größte Sorgfalt geachtet werden; da die optischen Eigenschaften der Transparentschicht in die Abtastung eingehen, so muß diese Transparentschicht einen genau definierten Brechungsindex (n = 1,46) aufweisen.

Das erfordert eine Fertigung in staubfreien Räumen. Der größte auftretende Höhenschlag am äußeren Plattenrand darf nur 0,5 mm betragen. Die Exzentrizität muß im Bereich von  $\pm$  50  $_{

m c}$ um liegen.

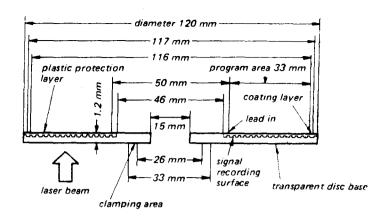

#### Struktur der Compact-Disc

Auf der Einlaufspur sind die Informationen über alle auf der Platte gespeicherten Titel enthalten. Die CD besitzt ca. 20.000 Spuren auf einer nur 33 mm breiten Programmfläche.

Erklärungen zu Abb.

transparent disc base

: Transparentschicht

diameter

: Durchmesser

plastic protection-layer

: Kunststoffschutzschicht

laser beam

: Laserstrahl

clamping area

: Arretierungsbereich der Zentrier-

mechanik

lead-in

: Einlaufspur

program area

: Programmbereich

signal recording surface

: Informationsebene (Programmebene)

#### Die Pits

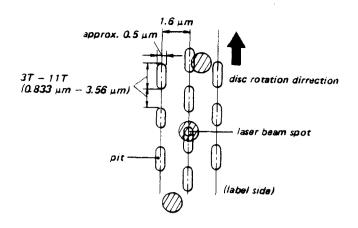

Die digitalen Daten sind durch die Pit-Länge und den Abstand zwischen den Pits definiert. Die Pits sind spiralförmig auf die Informationsebene (Programmfläche) aufgebracht und verlaufen aus der Sicht des Laserstrahls gegen den Uhrzeigersinn. Die Informationsdichte beträgt ca. 810 KBits/mm². Umgerechnet auf eine komplette CD ergibt das ca. 7 x 10<sup>9</sup> Bits. 30 Spuren auf der Programmfläche haben eine Breite von ca. 50 /um, was ungefähr der Dicke eines Menschenhaares entspricht. Der Spurabstand beträgt ca. 1,6 /um. Ein Pit hat eine Breite von 0,5 /um, die Länge variiert zwischen 0,833 - 3,56 /um.

Die Tiefe eines Pits beläuft sich auf 0,11 <sub>/</sub>um.

#### Die konstante Lineare (Abtast-) Geschwindigkeit

Für das CD-System sind zwei konstante lineare Geschwindigkeiten (Constant linear velocity = C.L.V.) vorgesehen.

In Abhängigkeit der gewählten Geschwindigkeit ändern sich auch die min. und max. mögliche Pitlänge, die max. Spielzeit und die Umdrehungszahl (innen und außen) der Platte.

$C.L.V._1 = 1,2 \text{ m/sek.}$

max. Plattendrehzahl (innen): 486 U/min min. dito (außen): 196 U/min max. Spielzeit: 74 Minuten min. Pitlänge: 0,833 /um max. Pitlänge: 3,05 /um

$c.l.V._2 = 1.4 \text{ m/sek.}$

max. Plattendrehzahl (innen): 568 U/min min. dito (außen): 228 U/min max. Spielzeit: 63 Minuten min. Pitlänge: 0,972 /um max. Pitlänge: 3,56 /um

Die minimale Pitlänge entspricht auch dem min. Pitabstand in der Spur, die max. Pitlänge dem größten Pitabstand.

#### Die Transparentschicht

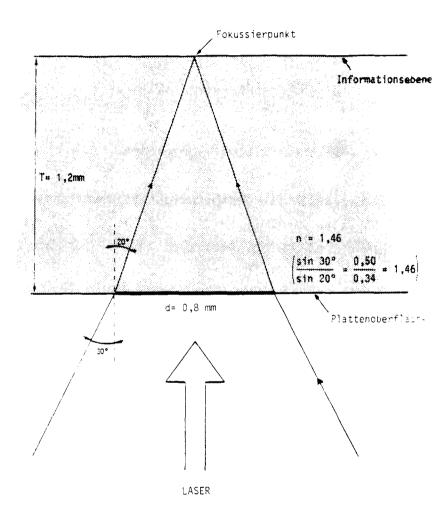

Die 1,2 mm dicke Transparentschicht hat eine sehr wichtige Furier tion. Eine Grundvoraussetzung hierfür ist ihr Brechungsinder in von 1,46. Wenn der Laserstrahl auf der transparenten Sterflatze auftrifft, hat er dort einen Durchmesser von ca. 0,8 mm.

Nach dem Durchdringen der transparenten Schicht trifft er auf die Informationsebene, wo er nur noch, bedingt durch den Brechungsmindex, einen Durchmesser von 1,7 jum aufweist. Hieraus resultiert auch, daß z.B. ein Staubkorn in der Größenordnung von weniger als 0,5 mm auf der Plattenoberfläche bei der Abtastung nicht mehr störend in Erscheinung tritt. Hieraus zeigt sich schon, daß z.B. CD, auch ohne Berücksichtigung der elektronischen Fehlenkorneitur, wesentlich unempfindlicher gegen mechanische Beschädigungen das eine herkömmliche analoge Schallplatte.

Der Brechungsindex n = 1,46 errechnet sich mit Hilfe der Ein- und Austrittswinkel zur Plattenoberfläche.

In der Abb. wird der Weg des Laserstrahls durch die Transparentschicht gezeigt. Es werden die Ein- und Austrittswinkel zur Plattenoberfläche und die unterschiedlichen Durchmesser des Laserspots auf der Plattenoberfläche und auf der Informationsebene dargestellt.

#### Das Auslesen der Pits

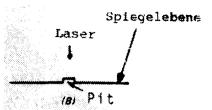

Die Pits und die Spiegelebene entsprechen den digitalen Daten "O" und "1". Bei der Abtastung eines Pits soll im Idealfall kein Licht reflektiert werden. Um das zu erreichen, muß die Pithöhe im direkten Zusammenhang mit der Wellenlänge des Laserlichtes und dem Brechungsindex "n" der transparenten Schicht stehen.

Die vereinfachte Formel hierzu lautet  $\frac{\lambda}{4}$ : n

Da der Durchmesser des Laserspot's auf der Informationsebene 1,7 um beträgt und somit größer ist als die Pitbreite von 0,5 um, wird sowohl von der Spiegelebene als auch von dem Pit Licht reflektiert. Aufgrund des direkten Zusammenhangs der Pithöhe zur Wellenlänge des Laserlichtes entsteht im Idealfall eine Phasendifferenz zwischen beiden reflektierten Strahlen von 2 x  $\frac{\lambda}{L}$  = 180°.

Es würde also eine Auslöschung (Interferenzeffekt) des reflektierten Lichtes stattfinden, sobald ein Pit abgetastet wird. In der Praxis tritt aber keine absolute Auslöschung der reflektierten Strahlen auf, jedoch reicht die Verminderung des reflektierten Lichtes aus, um eine Auswertung über eine Fotodetektoreinheit vorzunehmen.

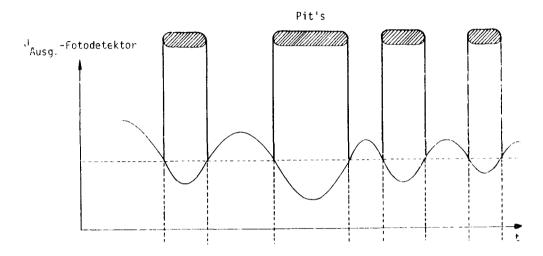

In Abhängigkeit der Pitlänge, die von 0,833 - 3,56 <sub>/um</sub> variieren kann, erfolgt eine Modulation des reflektierten Lichtes proportional zur Pitlänge.

Die Pithöhe ist bei der CD auf 0,11 jum festgelegt.

Folgende Abb. zeigt die Informationsebene mit einem Pit und der Spiegelfläche.

In der folgenden Abbildung zeigen wir die Signalspannung am Ausgang der Fotodetektoreinheit in Abhängigkeit der Pits auf der Informationsebene.

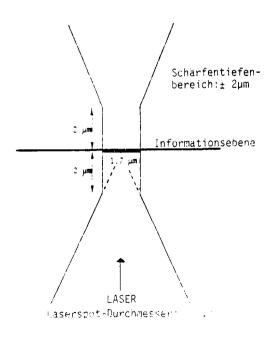

Um die Pits exakt auszulesen, ist eine genaue Fokussierung des Laserstrahls nötig. Die Fokussierung geschieht über das 2-Achsen-Element des optischen Abtastsystems, die Schärfentiefe beträgt 2,um.

In der Abb. werden der Laserspot und der Schärfentiefenbereich auf der Infoebene der CD dargestellt.

#### OPTISCHES ABTASTSYSTEM

Die technologische Verbindung der Optik und der Elektronik bezeichnet man als "Optoelektronik".

Es handelt sich hierbei um einen äußerst vielseitigen Bereich, der auch Phänomene wie z.B. die optische Strahlung, die Wechselwirkung zwischen Licht und Materie, Radiometrie, Fotometrie und die Eigenschaften der verschiedenen Quellen und Sensoren umfaßt.

#### Das Lichtspektrum

Die elektromagnetische Strahlung einer Lichtquelle wird anhand der Wellenlänge (Lambda =  $\lambda$ ) definiert. Die Frequenz einer elektromagnetischen Wellenlänge ergibt sich aus:

Der optische Bereich erstreckt sich von 10 nm bis 10<sup>6</sup> m. Er ist unterteilt in drei Kategorien:

- 1. Ultraviolette Strahlung (UV)

- 2. Sichtbares Licht

- 3. Infrarotstrahlung (IR)

Unter die Bezeichnung "Ultraviolett (UV)" fallen alle Wellenlängen, die unterhalb des sichtbaren Spektrums, aber oberhalb der Röntgenstrahlung liegen. Die Wellenlänge der UV-Strahlung liegt zwischen 10 und 370 nm. Alle Wellenlängen zwischen 350 – 750 nm sind für das menschliche Auge sichtbar.

Bei der Infrarotstrahlung handelt es sich um Wellenlängen, die oberhalb des sichtbaren Spektrums, aber noch unterhalb der Mikrowellen liegen  $(750 \cdot 10^{-9} \text{m bis } 10^{-3} \text{m})$ .

Eine Grundlage zum einwandfreien Auslesen der Informationen auf der CD ist ein "Licht" mit einer definierten Wellenlänge und Phasenlage. Die Lichtquelle sollte eine starke Richtwirkung besitzen. Alle diese Eigenschaften besitzt eine Laserlichtquelle, wodurch sie sich hervorragend zum Einsatz in ein solches optisches Abtastsystem eignet.

Für die Abtastung im CD-Player wird ein Halbleitenlaser (Laser-diode) mit einer Lichtausgangsleistung von 1 mW verwendet. Die Wellenlänge ( ) beträgt ca. 780 nm und liegt somit im IR-Benein

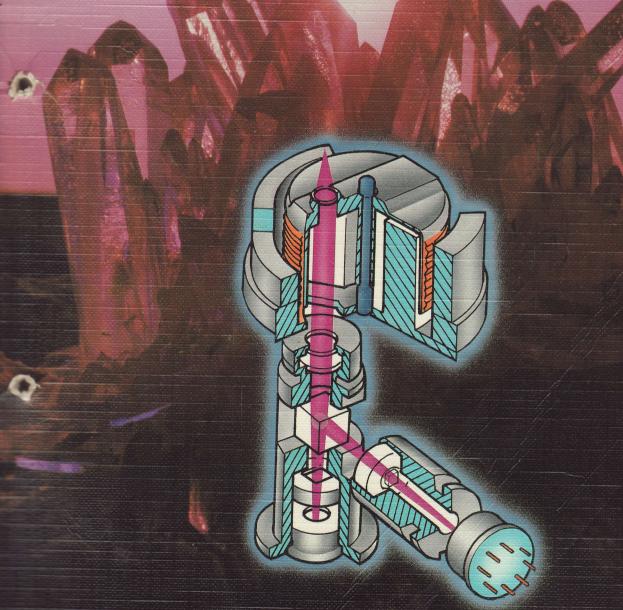

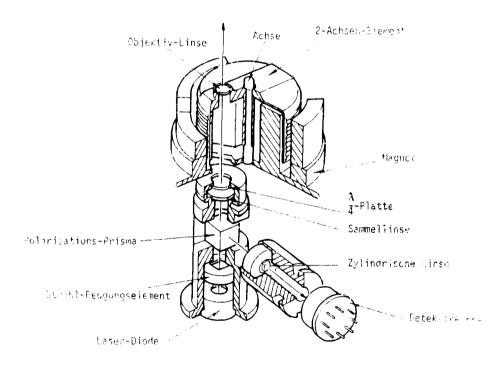

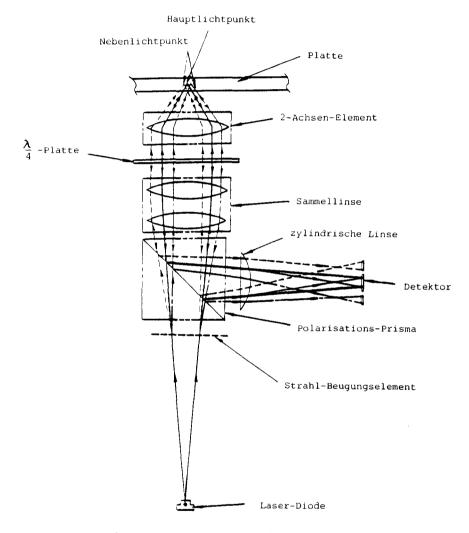

Die Abb. zeigt den Aufbau des optischen Systems des CDP-101.

im machfolgenden Text werden die wichtigsten Bauelemente der Optibeschnieben.

#### Die Injektions-Laser-Diode

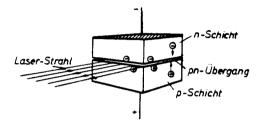

Im optischen Abtastsystem des CDP-101 wird ein Halbleiter-Laser verwendet. Prinzipielt können Halbleiter-Laser auf verschiedere Arten zum Aussenden von Laserlicht aktiviert werden. Ein sollner Laser kann z.B. mit Licht, Elektronenstrahlen oder elektr. Streenregt werden.

Die am meisten angewandte Art ist die der Injektion von Elektronen durch einen elektr. Strom (daher = Injektions-Laser).

Wird eine Anordnung, wie sie auf Abb. 10 gezeigt wird, von einem elektrischen Strom durchflossen, so rekombinieren "Elektronen" und "Löcher" in der Grenzschicht (PN-Übergang) und geben spontan Licht ab. Ab einer gewissen Stromstärke kommt es im PN-Übergang zu einer Umkehrung, wodurch die Lichtemission unterstützt wird.

Das spontan erzeugte Licht wird zusätzlich noch über 2 Spiegelflächen umgelenkt, es findet intern eine Lichtoszillation statt, die die Rekombination im PN-Übergang nochmals unterstützt (Erregung durch Licht). Die Frequenz der internen Oszillation beträgt ca. 100 MHz, sie ist nicht zu verwechseln mit der Frequenz bzw. Wellenlänge des austretenden Lichtes.

Vorteile einer Injektions-Laser-Diode:

- 1. Von der Bauart ist es die kleinste Laser-Lichtquelle.

- 2. Sie kann z.B. wie ein Transistor in Serie gefertigt werden.

- 3. Sie hat einen großen Wirkungsgrad.

#### Marum wird zum Auslesen der CD-Information ein Laser benötigt?

Das Licht aus üblichen Quellen, z.B. Sonne, Glühbirne und Gasentladungslampen, besteht im allgemeinen aus mehreren verschiedenen Wellenlängen und breitet sich nach allen Seiten gleichmäßig aus. Es ist bei dieser Lichtart nicht möglich, zwischen den Wellenzügen eine räumliche oder zeitliche feste Beziehung zu finden, es handelt sich hier um inkohärente Wellenzüge. Inkohärentes Licht wird bei einer spontanen thermischen Emission erzeugt. Für die beim CD-Player verwendete Optik benötigt man jedoch ein Licht mit definierter Wellenlänge und Phasenlage, sogenanntes kohärentes Licht.

Zwei oder mehrere Wellenzüge sind zeitlich kohärent, wenn sie über eine definierte Zeitdauer eine feste Phasendifferenz einhalten.

Daraus ergibt sich aber auch, daß diese Wellenzüge die gleiche Frequenz aufweisen müssen. Ein solches Licht erhält man auron induzierte oder stimulierte Emission, z.B. an einem PN-Übergarg, wie es bei der Injektions-Laserdiode geschieht.

Mit kohärentem Licht besteht dann die Möglichkeit, z.B. nach einer Reflexion durch eine entsprechende Optik eine Auswertung der Phasenlage bzw. der Polarisationsebene vorzunehmen und so den Original- und den reflektierten Lichtstrahl voneinander zu trennen. Ähnliches geschieht u.a. in der Optik des CD-Players, so daß nier nur ein kohärentes Licht, also ein Laserlicht verwendet werden kann.

#### A P C - Schaltung zur Steuerung der Laserdiode

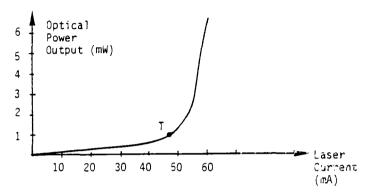

Während des Betriebs der Laserdiode muß der Stromfluß des externangelegten Gleichstroms einen definierten Schwellwert erreicren, bevor ein Laserstrahl abgegeben werden kann.

Unmittelbar nach Erreichen des Schwellwertes arbeitet der Laser stabil und sendet einen konstanten Lichtfaden aus. Bei zunehmender Strom steigt die Lichtausbeute extrem schnell an, und es bestert die Gefahr der Zerstörung.

Die Injektions-Laser-Diode (ILD) reagiert empfindlich auf Temperatur- und Stromschwankungen, daher muß zur Sicherheit die Lichtemission kontrolliert und durch eine Rückkopplungsschleife der extern angelegte Gleichstrom entsprechend nachgeregelt werden. Hinzukommt, daß die ILD dazu neigt, mit zunehmender Betriebsdauer die Lichtemission zu verringern.

Außerdem verringert sich die Lebensdauer drastisch, wenn die ILD konstant mit überhöhtem Strom "gefahren" wird. Aus diesen Gründen sorgt die APC-Schaltung (Automatic Power Control) für eine konstante Lichtemission über einen langen Zeitraum (ca. 4000 – 5000 Betriebsstunden).

Die Abb. zeigt die typische Betriebskurve einer ILD. Beachten Sie den als "T" im gekrümmten Bereich der Kennlinie eingezeichneten Schwellwert.

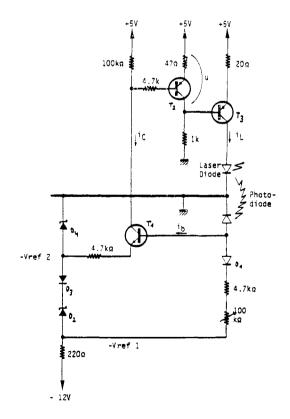

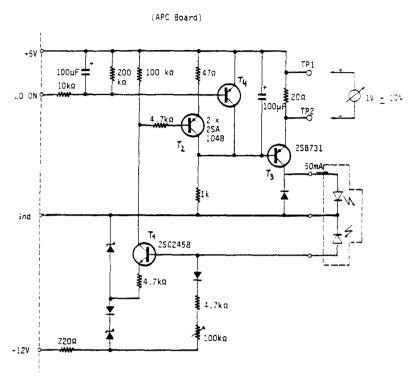

#### Opto-Feedback in der APC-Schaltung

Die Laser- und die Fotodiode sind, zur Kontrolle der Lichtausgangsleistung, mechanisch in einem Gehäuse untergebracht.

Steigt nun die Lichtausgangsleistung im Betrieb an, steigt ebenfalls die Basisspannung von der Transistor aufgeregelt, wodurch die Basisvon T<sub>2</sub> spannung sinkt, pnp-Transistor ist, ein wird seine Kollektorspannung und damit auch die Basisspannung von T<sub>z</sub> positiver. T<sub>3</sub> Transistor wird (pnp), steuert wodurch Strom durch die Laserdiode abnimmt.

Die Dioden  $D_2$ ,  $D_3$  und  $D_4$  sorgen für eine konstante Referenzspannung am Emitter des Transistors  $T_1$ ;  $D_3$  speziell hat die Aufgabe, den Temperaturkoeffizienten der Zenerdioden zu kompensieren. Die Einstellung des Arbeitspunktes der Laserdiode erfolgt über den Basisstrom von  $T_1$ , die Justage wird in der Fabrikation eingestellt und sollte nicht verändert werden!

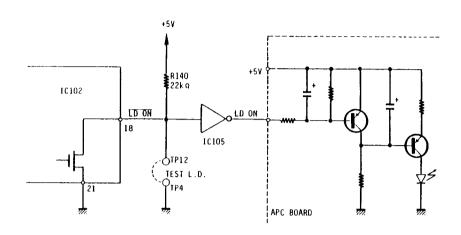

Hinzugekommen ist nun der Transistor  $T_4$ . Er hat die Aufgabe, die ILD ein- bzw. auszuschalten. Wenn an der Basis von  $T_4$  über der Inverter IC105 Punkt 12 ein "L" ansteht, wird die Basis von  $T_3$  über die Kollektor/Emitter-Strecke auf +5V gelegt, so daß  $T_3$  gesperrt ist und kein Strom durch die Laserdiode fließt. Erst bei einem "H"-Pegel an der Basis von  $T_4$  kann die Basisspannung vor  $T_3$  so weit absinken, daß ein Stromfluß über  $T_3$  durch die ILD erfolgt.

Die Ansteuerung von  $T_4$  erfolgt von PIN 18 des IC102 über den Inverter IC105 (s. Abb.). Zur Kontrolle kann am Emitterwiderstand von  $T_3$  mit Hilfe des Spannungsabfalls der Stromfluß durch die ILD überprüft werden, der Spannungsabfall über den Widerstand (TP1 und TP2) sollte 1 Volt betragen, was einem Strom von 50 mA entspricht.

Durch Brücken der Testpunkte 12 und 4 kann der Laser aktiviert werden.

LASER DIODE ON/OFF CONTROL

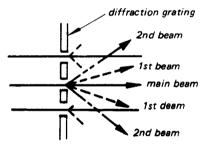

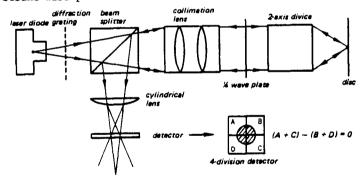

#### Das Strahlbeugungselement (diffraction grating)

In der Abb. wird die grundsätzliche Funktion des Strahlbeugungselementes dargestellt.

1st beams are used for tracking servo.

Wenn ein Lichtstrahl durch einen schmalen Schlitz austritt, erhält man an der Austrittsöffnung neben dem Hauptstrahl mindestens 2 Nebenstrahlen. Der sogenannte erste Nebenstrahl besitzt 25% der Energie des Hauptstrahles. In der Optik des CDP-101 werden die Nebenstrahlen erster Ordnung zur Trackingregelung (Spurnachführung) verwendet.

#### Polarisationsprisma

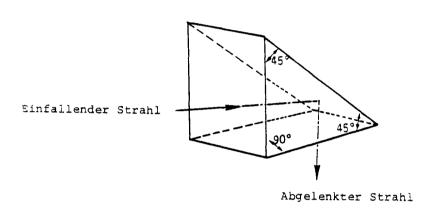

Ein Prisma ist ein optisch transparenter Körper, der zum Brechen, Streuen oder Reflektieren eines Lichtstrahls eingesetzt wird. Die einfachste Form eines solchen Prismas ist das rechtwinklige Prisma.

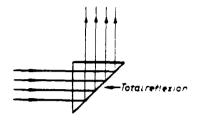

Ein Lichtstrahl, der mit einem Winkel von 90<sup>°</sup> auf eine der Stirnflächen (Katheten) des Prismas auftrifft, wird innen an der Hypotenuse vollständig reflektiert (Totalreflexion), um 90<sup>°</sup> abgelenkt und tritt dann aus der zweiten Stirnfläche wieder aus.

Um Lichtverluste zu vermeiden, werden Kathetenflächen entspiegelt. Da der Reflexionswinkel von der Lage des Prismas zur optischen Achse abhängig ist, ist eine genaue (werksseitige) Justage Voraussetzung.

Die Wirkung des Polarisationsprismas beruht auf dem Brewsterscher Gesetz. Es besagt, daß bei der Reflexion unter einem bestimmter Winkel (dem sog. Brewsterschen Winkel), bei dem das reflektierte Licht vollständig linear polarisiert wird, der reflektierte und der gebrochene Strahl senkrecht aufeinanderstehen.

Zur Errechnung des Brewsterschen Winkels gilt:

$$\tan \mathbf{k}_{B} = \frac{n2}{n1}$$

Gleichzeitig sagt dieses Gesetz auch, daß linear polarisiertes Licht, dessen elektr. Vektor in der Einfallebene schwingt, verlustfrei durch die Grenzschicht zweier Materien geht, wenn es unter dem Brewsterschen Winkel einfällt. Der reflektierte und der gebrochene Strahl stehen in diesem Fall senkrecht zueinander, die reflektierte Intensität ist Null.

Ein Polarisationsprisma besteht im allgemeinen aus zwei rechtwinkligen Prismen, hergestellt aus unterschiedlichen Materialien. Ein

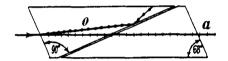

senkrecht auf die Kathetenfläche des oberen Prismas einfallender Lichtstrahl "A" wird an der Brechungskante "O", die gleichzeitig der optischen Achse entspricht, in zwei Strahlen aufgespalten. Der sogenannte "außerordentliche Strahl" (a) erfährt fast keine Ablenkung. Der "ordentliche Strahl" (b) wird seitlich abgelenkt.

Der "außerordentliche Strahl" durchläuft also das Polarisationsprisma nahezu ohne Ablenkung, erfährt jedoch eine lineare Polarisierung. Eine besondere Art eines Polarisationsprismas stellt das sogenannte "Nicolsche-Prisma" dar.

Das Licht, das parallel zu den Längskanten einfällt, wird auch hier in zwei Strahlen aufgeteilt. Der ordentliche Strahl (0) wird seitlich abgelenkt und von den geschwärzten Außenflächen absorbiert. Es tritt hier nur der außerordentliche unabgelenkte, jedoch linear polarisierte Strahl (a) aus.

Das von der CD reflektierte Licht durchläuft auf seinem gesamten  $\frac{\lambda}{2}$ -Scheibe, wodurch die Polarisationsebene gedreht ist. Beim Auftreffen auf das Polarisationsprisma erfährt das reflektierte und in der Polarisationsebene gedrehte Licht eine Totalreflexion, so daß es auf die Detektoreinheit abgelenkt wird.

Die Wirkung des Polarisationsprismas in der Optik des CD-Players ist nur im Zusammenhang mit der  $\frac{\lambda}{4}$ -Platte zu erklären.

#### <del>\_\_\_</del>Platte

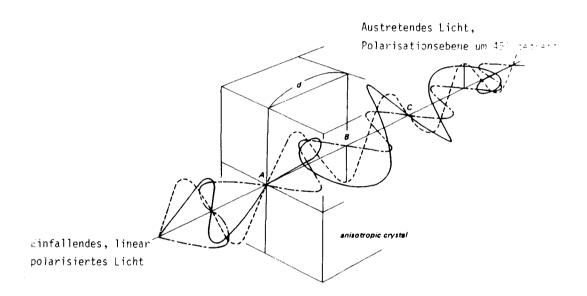

Zur Drehung der Polarisationsebene des Lichtes um ca.  $45^{\circ}$  verwendet man einen speziellen Kristall (anisotropic crystal) mit unterschiedlichen Beugungsindizes in den elektr. Feldebenen X und Y. Beim CDP-101 passiert der Lichtstrahl zweimal die  $\frac{\lambda}{4}$ -Platte, so daß die Polarisationsebene insgesamt um  $90^{\circ}$  gedreht wird. Aufgrund dieser Drehung der Polarisationsebene kann am Polarisationsprisma der CD-Optik das vom Laser einfallende und das von der CD reflektierte Laser-Licht aufgeteilt werden.

Drehung der Polarisationsebene durch einen anisotropen Krista...

Die Fortpflanzungsgeschwindigkeit des Lichtes mit dem Ausgangspunkt "A" verändert sich aufgrund der unterschiedlichen Beugungsindizes in der (elektr.) X- und Y-Ebene.

An Punkt "A" eintretendes, linear polarisiertes Licht durchläuft den anisotropen Kristall mit der Dicke "d" und tritt an Punkt "B" mit einem Phasenverschub von  $90^{\circ}$  aus (daher  $\frac{\lambda}{\lambda} = 90^{\circ}$ ).

Das hier austretende Licht ist zirkular polarisiert, die Polarisationsebene um 45° gedreht. Befände sich beispielsweise der Lichtaustritt an Punkt "C", so wäre das austretende gleich dem an Punkt "A" eintretenden, linear polarisierten Licht.

Die in der Laser-Optik verwendete  $\frac{\lambda}{4}$ -Platte hat die Dicke "d", was einem Lichtaustritt an Punkt "B" entspricht.

Da der Lichtstrahl innerhalb der Optik zweimal die  $\frac{\lambda}{4}$ -Platte passiert, erhält man nach dem zweiten Lichtaustritt wiederum ein Linear polarisiertes Laserlicht mit einer um 90° gedrehten Polarisationsebene.

#### Die Sammellinseneinheit

Ein Laserstrahl hat den Nachteil, daß sein Durchmesser nach dem Austritt aus der Laserdiode sehr gering ist und der Strahl in sich eine auseinanderstrebende Tendenz (Divergenz) aufweist.

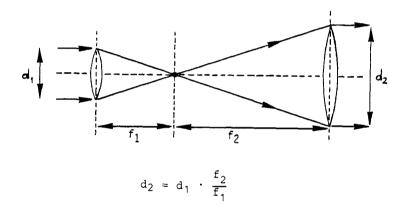

Durch eine Anordnung von 2 bikonvexen Linsen, wie in der Abb. gezeigt, läßt sich der Strahldurchmesser erhöhen und die Divergenz reduzieren. Eine solche Linsenanordnung wird auch als "Keplersches Fernrohr" bezeichnet.

Sie wird in der Optik des CDP benutzt, um einen parallel gerichteten Laserlichtstrahl mit definiertem Durchmesser zu gewinnen, der dann durch das 2-Achsen-Element auf die CD fokussiert wird.

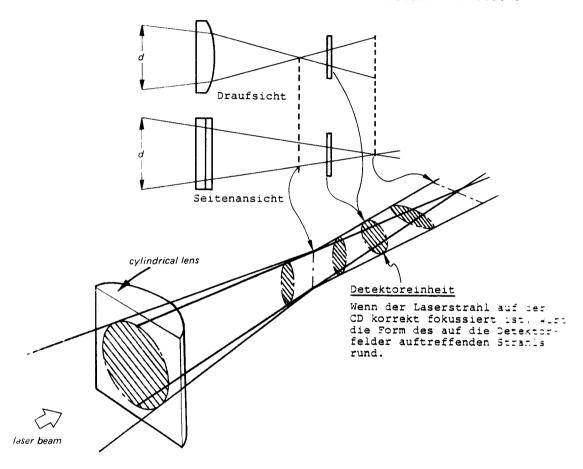

#### Zylindrische Linse

Es ist die Aufgabe dieser Linse, in Verbindung mit der 4-teiligen Detektoreinheit den Fokussierzustand des Laserspots auf der CD zu erkennen.

Tritt der Laserstrahl durch die zylindrische Linse, so wird er nur in der Horizontalen fokussiert. Aus diesem Grunde hat der Strant nach dem Passieren der Linse einen elliptischen Querschritt. Diese elliptische Form ist abhängig von der Fokussierung des Laserstrahls durch das 2-Achsen-Element und somit direkt abhängig von der Fokussierung des Laserstrahls auf der CD. Setzt man voraus, daß der Krümmungsgrad der zylindrischen Linse bekannt ist, so läßt sich anhand der Strahlform der Fokussierzustand ermitteln.

#### **Fokusdetektor**

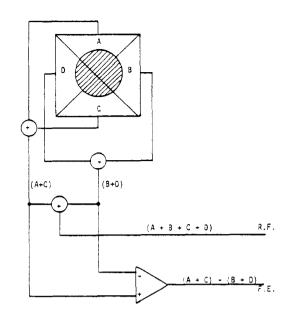

Der aus 4 einzelnen Detektorfeldern bestehende Fokusdetektor ermittelt den Fokussierzustand anhand der Form des Strahllancepunktes auf dem Detektor.

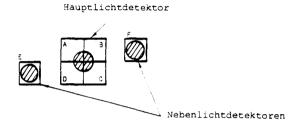

Die Ausgänge der 4 Detektorfelder des Hauptlichtdetektors A, B, C und D ermitteln sowohl den Signalinhalt (RF) als auch den Fokussierzustand.

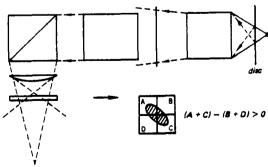

Die Ausgangsspannungen einzelnen Detektorfelder sind proportional zur Strahllandefläche. Die Auswertung der über Spannungen erfolgt Additions- und Subtraktionsstufen zur Ansteuerung des 2-Achsen-Elementes nach der Formel (A+C) - (B+D). Die Auswertung des Signalinhaltes erfolgt über eine Addition In der Abb. von A+B+C+D. sehen Sie das Grundprinzip.

In Abb. a-c sehen Sie eine schematische Darstellung der Erkennung und Gewinnung des Fokuszustandes bzw. der Nachregelspannung für das 2-Achsen-Element.

a) Der Strahl wird präzise auf die CD-Informationsebene fokussiert.

b) Die Entfernung zur CD ist zu gering.

c) Die Entfernung zur CD ist zu groß.

Bei der optimalen Fokuseinstellung ist die Nachregelspannung für das 2-Achsen-Element gleich Null und die auf die Detektorfläsnen auftreffende Strahlform rund.

#### Tracking-Detektor

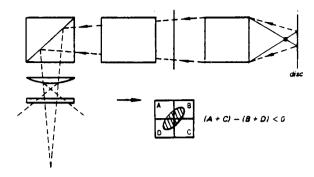

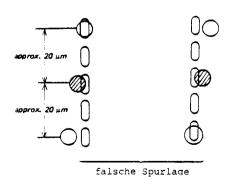

Mit Hilfe der Nebenlichtdetektorfelder E und F wird die Spurfurrung ermittelt. Bei **optimaler** Spurführung wird das jeweils vor und hinter dem abgetasteten Pit liegende, übernächste Pit am rechter

bzw. linken Rand von dem jeweiligen Nebenstrahl erfaßt, so daß die reflektierten Seitenstrahlen an den Nebenstrahldetektoren jeweils die gleiche Ausgangsspannung verursachen.

korrekte Spurlage

In der folgenden Abb. sehen Sie die beiden möglichen Spurfehler, in beiden Fällen liegt der Hauptstrahl nicht korrekt auf der abzutastenden Pit.

-- 26 ---

Einer der beiden Nebenstrahlen trifft in diesen Fällen auf die Spiegelfläche, der andere direkt auf ein Pit, entsprechend ergibt sich an einem Nebenstrahldetektor eine Ausgangsspannung, an dem zweiten jedoch nicht. Da die Auswertung der Ausgangsspannungen der beiden Nebenlichtdetektorenfelder E und F über einen Differenzverstärker erfolgt, erhält man bei Spurabweichungen eine Nachregelspannung, deren Polarität proportional zur Richtung (rechts oder links neben der Spur) und zur Größe der Spurabweichung ist. Die folgenden Abb. zeigt die Anordnung der Detektorfelder.

#### Das 2-Achsen-Element

Damit die Pits exakt auszulesen sind, muß der Laserstrahl konstant auf die Pitspur fokussiert werden. Aus diesem Grunde wird die Optik durch ein Servosystem axial in 2 Ebenen bewegt.

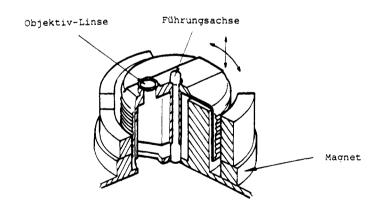

Es kann also der Abstand der Optik zur Platte zum Einstellen der Fokussierung verändert und die Optik seitlich, zur Spurnachführung, bewegt werden. Die Abb zeigt den Aufbau des 2-Achsen-Elementes mit Fokussieroptik.

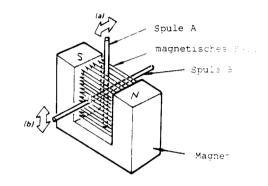

Das 2-Achsen-Element arbeitet mit zwei unterschiedlichen Spulen. Die für die Spurnachführung verantwortliche Spule ist wie eine Lautsprecherspule gewickelt. Diese Spule/Magnetanordnung arbeitet ähnlich wie ein Drehspuleninstrument. Die Fokus-Spule ist vertikal gewickelt. Durch den Stromfluß in den Spulen läßt sich das 2-Achsen-Element steuern.

In der Abb. ist das Funktionsprinzip des 2-Achsen-Elementes dargestellt:

Fließt ein Strom durch die Spule "A", so tritt eine Kraftwirkung in Richtung "a" auf. Der Stromfluß durch Spule "B" erzeugt eine Kraft in Richtung "b".

#### Der Weg des Laserlichtes durch das optische System

In der nachfolgenden Abb. ist der Weg des Laserstrahls durch das optische Abtastsystem dargestellt.

Nach dem Austritt aus der Laser-Diode passiert der Strahl das sogenannte Strahl-Beugungselement (diffraction grating).

Seine Aufgabe ist es, die sogenannten Nebenstrahlen zu erzeugen, die zur Spurnachführung (tracking) verwendet werden. Es handelt sich hierbei um zwei Nebenstrahlen erster Ordnung, die in einem zum Hauptstrahl abweichenden Winkel austreten.

Als nächstes geht das Laser-Licht ohne Ablenkung durch das Polarisationsprisma. Nach dem Austritt aus diesem Prisma ist es linear polarisiert. Die Lichtstrahlen treffen nun auf die Sammellinseneinheit. Hier werden die bisher divergenten Strahlen parallet gerichtet.

Da diese Sammellinsenanordnung nach dem Prinzip des "Keplerschen Fernrohrs" arbeitet, weisen die Lichtstrahlen beim Austritt auch einen größeren **definierten** Durchmesser auf.

Die parallel gerichteten Strahlen durchlaufen dann zum erstenmal die  $\frac{\lambda}{4}$ -Platte, wobei die Polarisationsebene um 45 $^{\rm O}$  gedreht und das Licht zirkular polarisiert wird.

Das nachfolgende 2-Achsen-Element fokussiert die Strahlen exakt auf die CD.

Die von der CD reflektierten Laserstrahlen durchlaufen auf dem "Rückweg" abermals das 2-Achsen-Element und treffen dann zum zweitenmal auf die  $\frac{\lambda}{2}$ -Platte.

Das noch zirkular polarisierte Licht wird nun wieder linear polarisiert und die Polarisationsebene dreht sich nochmals um 45°.

Danach durchläuft das Licht die Sammellinseneinheit und trifft dann linear polarisiert, mit jedoch um 90° gedrehter Polarisationsebene auf das Polarisationsprisma. Bedingt durch die um 90° gedrehte Ebene erfährt das Laserlicht eine Totalreflexion, wodurch die von der CD kommenden Laserstrahlen auf die Detektoreinneit abgelenkt werden.

#### CD-Aufnahmeverfahren

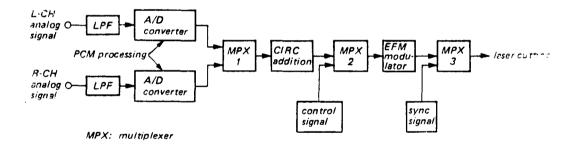

Die analogen Signale werden getrennt nach rechtem und linkem Kanalüber je ein Tiefpaßfilter den A/D-Wandlern zugeführt. Hier erfolgt die Umwandlung des analogen Signals in ein PCM-Signal.

Im nachfolgenden MPX-1-Block werden die PCM-codierten Informationen der beiden Kanäle im Multiplexverfahren ineinander verschacttelt. Der CIRC-Block hat die Aufgabe, Daten, die eine wirkungstvolle Fehlererkennung und -korrektur ermöglichen, dem Signalbeizufügen.

Das sogenannte Kontrollsignal (Steuersignal) – es besteht aus 98 Symbolen und enthält u.a. die Ein- und Auslauf-, Titel-, Zeit- und Preemphasiskennung – wird im MPX-2-Block (Multiplexing) hinzugefügt.

Danach erfolgt eine 8-auf-14 Bit-Umsetzung im EFM-Modulator. Zum Abschluß wird wiederum im Multiplexverfahren das Synchron-Signal beigefügt, das zur Steuerung der Abtastgeschwindigkeit und somit zur Synchronisierung des Plattenservos dient. Das so vervollständigte Signal wird zur Herstellung des Plattenmasters verwendet.

#### Theorie der PCM-Technik

#### Analog/Digital-Umwandlung

Ein analoges Signal muß zuerst in ein digitales Signal umgewandelt werden, ehe es digital zu verarbeiten ist.

Die A/D (analog/digital) und auch die D/A (digital/analog) -Umwandlung ist technisch relativ schwierig zu realisieren, daher setzen diese Umwandlungsstufen die Grenzen fest für die Leistungsfähigkeit des ganzen Systems.

Die A/D-Umwandlung erfolgt in mehreren Schritten:

- 1. Filterung (Tiefpaß)

- 2. Abtastung

- 3. Quantisierung

- 4. Codierung

Abtastung: Das Prinzip der Abtastung basiert auf dem Shannon-Lehrsatz (auch Nyquist-Lehrsatz genannt).

Er besagt: Ein kontinuierlich mit der Zeit verlaufender Vorgang läßt sich in eine Folge von zeitdiskreten Mustern umwandeln, wenn

die Frequenz, mit der die Probeentnahme erfolgt, mindestens doppelt so groß ist wie die höchste im abzutastenden Signal enthaltene Frequenz.

Wie kann man diese Theorie zur A/D-Wandlung anwenden?

Ein Audiosignal (analog) ändert sich kontinuierlich mit der Zeit! Um es in ein digitales Signal umzuwandeln, muß man es zuerst einmal abtasten, d.h. zu bestimmten Zeitpunkten eine Probe des Pegelwertes nehmen. Die Zeitintervalle zwischen den entnommenen Proben nennt man Abtastintervalle ( $t_s$ ), sie sollten konstant sein.

Der Vorgang des Abtastens scheint zwar auf den ersten Blick eine starke Verzerrung des Originals zur Folge zu haben, weil Veränderungen zwischen den Abtastzeitpunkten nicht erkannt werden.

Tatsächlich läßt sich jedoch nachweisen, daß die Abtastung mit festen Abtastintervallen keinerlei Informationsveränderung zur Folge hat. Voraussetzung hierfür ist, daß die Abtastfrequenz mindestens doppelt so hoch ist wie die max. auftretende Informationsfrequenz.

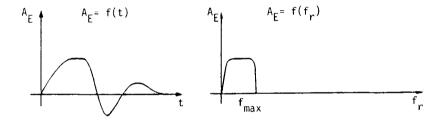

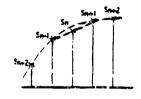

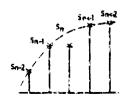

Zum besseren Verständnis sehen Sie in den folgenden Abbildungen mehrere Darstellungen, die sowohl den zeitlichen Verlauf eines Signals als auch den Amplitudenverlauf zur Frequenzachse (Spektrum) zeigen!

Die Abb. zeigt ein analoges Eingangssignal. Daneben sehen Sie das Frequenzspektrum des gleichen Signals. Oberhalb der max. Frequenz (fmax) ist keinerlei Energie vorhanden (Bandbreitenbegrenzung).

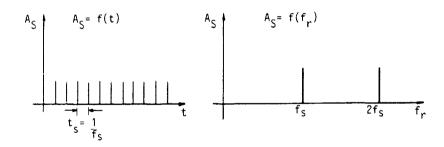

In diese Abb. ist das Abtastsignal dargestellt. Es handelt sich hierbei um eine Impulsfolge mit der Frequenz "fs". Der Impulsabstand "t $_{\rm S}$ " (Abtastintervall) ergibt sich aus dem Kehrwert der Abtastfrequenz (t $_{\rm S}=\frac{1}{7}$ s). Daneben ist das Spektrum dieser-Impulsfolge dargestellt.

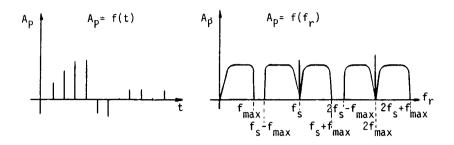

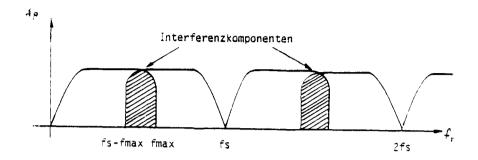

Das aus der Abtastung resultierende Signal und dessen Frequenzspektrum zeigt die folgende Abb.

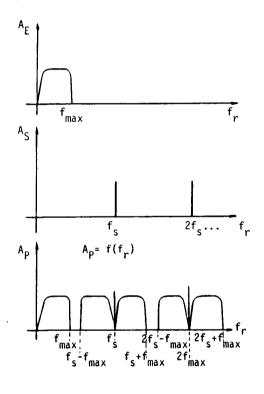

In der unteren Abb. sehen Sie noch einmal alle drei Diagramme der Spektren untereinander:

Man erkennt klar, daß das Spektrum des abgetasteten Eingangssignals völlig dem des Originals entspricht, sich jedoch mit dem Vielfachen der Abtastfrequenz (f<sub>s</sub>) wiederholt. Mit einem geeignetem Tiefpaßfilter ist es möglich, nur das Frequenzspektrum des Eingangssignals herauszufiltern und die Vielfachen zu unterdrücken.

Aus dieser Abb. ist aber auch ersichtlich, warum die Abtastfrequenz "f " größer sein muß, als das Doppelte der höchsten im Eingangssignal enthaltenen Frequenz.

Wenn diese Voraussetzung nicht gegeben ist, tritt eine Interferenzbildung (in der Graphik als Überlappungszone ersichtlich) zwischen dem Original-Spektrum und dem sich mit "f<sub>s</sub>" wiederholenden modulierten Signal auf. Eine Herausfilterung der hieraus entstehenden Differenzfrequenz ist nachträglich nicht mehr möglich.

Folgende Abb. zeigt die Interferenzbildung, wenn die Abtastfrequenz kleiner als 2 x  $f_{\text{max}}$  ist.

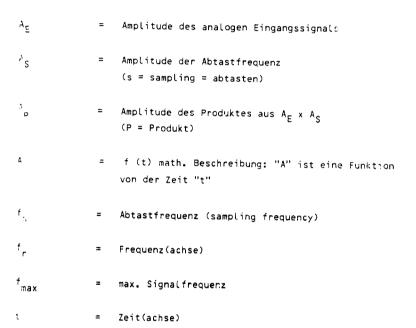

Zeichenerklärung zu den vorherigen Abbildungen:

Das Phänomen der Interferenzbildung wird auch als "Aliasing" bezeichnet.

Wenn man nun eine Abtastfrequenz (sampling frequency) festiegt, muß auch sichergestellt werden, daß die abzutastende Eingangssignalfrequenz um mehr als die Hälfte niedriger ist als die Abtastfrequenz ( $f_{max} = \frac{f_s}{2}$ ), um eine Interferenzbildung zu vermeiden.

Aus diesem Grunde muß ein sehr steiles Anti-Aliasing-Filter (Interferenzunterdrückungsfilter) in den Signalweg geschaltet werden.

Die höchste zu berücksichtigende Audiofrequenz beträgt nun 22 kHz. Bei einer  $f_{\rm max}$  von 22 kHz muß also die Abtastfrequenz 44 kHz betragen.

Da gleiche Kriterien auch für die Abtastfrequenz beim PCM-Prozessor vorliegen, hier jedoch noch die jeweilige Fernsehnorm eingeht, wurde für PCM-Systeme nach CCIR eine Abtastfrequenz von 44,1 kHz festgelegt! Diese Abtastfrequenz wurde auch für das von SONY und Philips entwickelte CD-System übernommen.

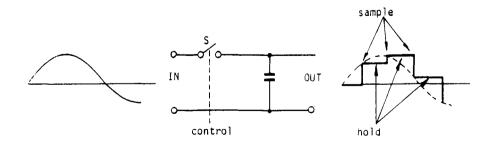

## Sample-Hold-Circuit (Abtast- und Haltespannung)

Nachdem zuvor die Abtasttheorie erläutert wurde, wollen wir nun feststellen, wie dieser Vorgang zur A/D-Wandlung genutzt wird.

In der Praxis wird mit sogenannten Sample-Hold-Schaltungen gearbeitet. Die Abtast-Haltekreise haben zwei Grundfunktionen:

- Sie entnehmen dem Eingangssignal in periodischen Abständer pulsamplitudenmodulierte Abtastwerte.

- 2. Diese werden in einem Haltekreis gespeichert, um genügend Zeit für die Codierung zu garantieren.

Eine Sample-Hold-Schaltung ist im Prinzip ein Spannungsspeicher, der eine gegebene Spannung in einem hochwertigen Kondensator speichert.

Die Abb. zeigt die grundsätzliche Arbeitsweise dieser Schaltung.

Bei der Abtastung schließt der Schalter "S" vorübergehend; öffnet er sich wieder, so hält der Kondensator "C" die Spannung so lange, bis der Schalter erneut geschlossen wird und der Kondensator sich auf den neuen Abtastwert auflädt.

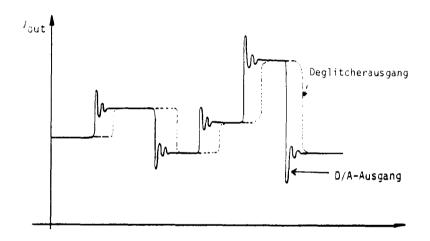

S/H-Schaltungen finden wir auch bei der D/A-Wandlung. Sie sind dort dem D/A-Wandler nachgeschaltet, um unerwünschte Spannungsspitzen am Ausgang der D/A-Wandlerstufe zu eliminieren. In diesem Fall wird die Schaltung als "Deglitcher" bezeichnet.

Folgende Abbildung zeigt die Funktion einer S/H-Schaltung, verwendet als "Deglitcher" hinter einen D/A-Wandler.

## Prinzip der Quantisierung und Codierung

Nach dem zuvor beschriebenen Abtastvorgang befinden wir uns immer noch im analogen Bereich, da die Amplituden der einzelnen Abtastwerte zwischen Plus und Minus eines bestimmten Maximalwertes theoretisch unendlich variieren können.

Nun folgt der entscheidende Schritt in den digitalen Bereich durch die Quantisierung, wobei man durch den Quantisierungsprozeß die unendliche Zahl der möglichen Abtastwerte auf eine endliche Zahl reduziert.

### Beispiel:

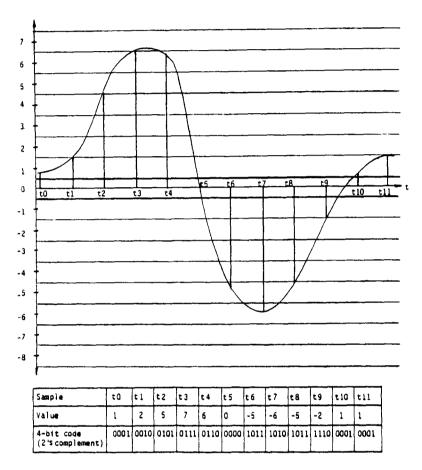

In diesem Fall, dargestellt in nachfolgender Abbildung, wird der Bewertungsbereich für das analoge Signal in 16 einzelne Werte aufgeteilt (quantisiert). Diese Werte werden dann in einen binären Code umgewandelt. Um 16 unterschiedliche Werte darzustellen (-8 bis  $\pm$ 7), benötigt man eine 4 Bit-Quantisierung (2<sup>4</sup> = 16).

Prinzip der Quantisierung und Codierung

sample

Abtastzeitpunkt

value

Wert

4-Bit-Code

(2's complement/4 Bit-Code) Zweierkomplement

## Codierung

Da das analoge Eingangssignal positive und negative Werte haben kann (bipolares System), verwendet man den Zweierkomplementcode, um eine Kennungsmöglichkeit der positiven und negativen Werte zu erhalten.

## Beispiele zur Bildung des Zweierkomplementcodes:

## **Quantisierungsintervalle**

Als Quantisierungsintervalle (Q) bezeichnet man den Zeitraum zwischen den Abtastzeitpunkten. Ein digitaler Wert, der einem bestimmten Quantisierungsintervall zugeordnet ist, soll den Wert in der Mitte des Intervalls (Q) darstellen. Die Quantisierung ist im Prinzip ein Vorgang, in dem ein Teil der Information nicht bewertet wird. Es wird nur ein Anteil verarbeitet, der zur Gewährleistung der gewünschten Klangqualität erforderlich ist.

## Quantisierungsfehler = Quantisierungsrauschen

Beim Quantisierungsvorgang als solchem handelt es sich um einen unlinearen Vorgang, da alle Werte eines Quantisierungsintervalls (Q) durch den Wert in der Mitte des Intervalls (Q) vertreten werden. Hieraus resultiert der sogenannte Quantisierungsfehler. Zwischen dem Quantisierungsfehler im digitalen System und dem analogen Rauschen eines Analog-Systems besteht ein sehr enger Zusammenhang.

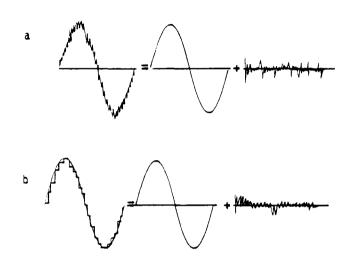

Das quantisierte Signal kann als ein Präzisionssignal plus Quantisierungsfehler betrachtet werden. Im Vergleich dazu kann man ein Analogsignal als Summe der rauschfreien Signale plus Rauschsignal betrachten.

Diese Betrachtungsweise sehen Sie in folgender Abbildung. Es wird klar, daß ein Quantisierungsfehler gleichzusetzen ist mit einer Quantisierungsrauschen.

Bei dem hier beschriebenen Quantisierungssystem handelt es sich un eine lineare Quantisierung, da alle Quantisierungsintervalle gleich sind.

Es ist also möglich, auch beim PCM-Systen einen Signal/(Quantisierungs-)Rauschabstand zu ermitteln (S/N-Ratio).

Er errechnet sich aus folgender Formel:

Bei einem 16-Bit-System ist also **theoretisch** ein S/N-Ratio vor. (6,02 x 16) + 1,76 = 98,08 dB möglich, bei einem 14-Bit-System wären es 86,04 dB.

## Fehlerkorrektur (CIRC)

Beim CDP wird eine Fehlerkorrektur nach dem "Cross-Interleave-Reed-Solomon-Code" durchgeführt. Das genaue Schema der Korrektur wird geheimgehalten, jedoch arbeitet dieses System grundsätzlich ähnlich wie das von anderen PCM-Produkten bekannte Cross-Interleave-System.

Nachfolgende Abbildung zeigt das Arbeitsprinzip des Cross-Codes in einer vereinfachten Darstellung.

| Мо | Di | Mi | Do | Fr | Sa | <u>so</u> |

|----|----|----|----|----|----|-----------|

| 27 | 28 | 29 | 30 | 1  | 2  | 3         |

| 4  | 5  | 6  | 7  | 8  | 9  | 10        |

| 11 | 12 | 13 | 14 | 15 | 16 | 17        |

| 18 | 19 | 20 | 21 | 22 | 23 | 24        |

| 25 | 26 | 27 | 28 | 29 | 30 | 31        |

| 25             | 18                   | 26 | 1 1 | 19 | 2 <b>7</b> | 4  |  |  |

|----------------|----------------------|----|-----|----|------------|----|--|--|

| 12             | 20                   | 28 | 27  | 5  | 13         | 21 |  |  |

| 29             | Mo                   | 28 | 6   | 14 | 22         | 30 |  |  |

| Di             | 29                   | 7  | 15  | 23 | 31         | Mi |  |  |

| 30             | 8                    | 16 | 24  | Do | 1          | 9  |  |  |

| 17             | Fr                   | 2  | 10  | Sa | 3          | So |  |  |

|                | Verschlüsselung nach |    |     |    |            |    |  |  |

| dem Cross-Code |                      |    |     |    |            |    |  |  |

| 25 | 18 | 26 | 11 | 19 | 27 | 4  |

|----|----|----|----|----|----|----|

| 12 | 20 | 28 | 27 | 5  | 13 | 21 |

| 29 | Mo | 28 | 6  | 14 | 22 | 30 |

| Di | 29 | 7  | 15 | 23 | 31 | Mi |

| 30 | 8  | 16 | 24 | Do | 1  | 9  |

| 17 | Fr | 2  | 10 | Sa | 3  | So |

|    |    |    |    |    |    |    |

4 5 6 7 8 9 10

11 12 13 14 15 16 17

18 19 20 21 22 23 24

25 26 27 28 29 30 31

Datenfehler nach der becodierung. Leichte Korrrektur der einzelnen Fehr

Mo Di Mi Do Fr Sa So

**28** 29 30

ler möglich.

Ausfall einer Datenzeile durch Dropout des Bandes oder mechanische Beschädigung der Compact-Disc

Die Reihenfolge der Originaldaten wird nach einem bestimmten Schlüssel einem Raster zugeordnet. Wenn innerhalb dieses Rasters eine Datenzeile ausfällt, läßt sich der Daten-Inhalt anhand der anderen noch vorhandenen Datenzeilen errechnen.

## Interleave-System

Bei der Interleave-Methode werden die aufzuzeichnenden Wörter für eine feste Zeitdauer und in spezifizierten Intervallen verzögert. Bei der Wiedergabe wird umgekehrt verfahren.

In folgender Abbildung sehen Sie ein Beispiel:

| BI <b>€</b><br>BQ | ξ.    |               |            |       |              |       |        |       |      |

|-------------------|-------|---------------|------------|-------|--------------|-------|--------|-------|------|

| но ` .            | LO    | R-48          | L-95       | R-143 | t−190        | R-238 | P~288  | 0-336 | CRCC |

| H16               | L48   | R0            | L- 47      | R-95  | L-142        | R-190 | P~240  | Q-288 | CRCC |

| <b>⊣</b> 32       | 96    | ₹48           |            | R-47  | i-9 <b>4</b> | R-+42 | P~ 192 | Q-240 | CRCC |

| <b>⊣48</b>        | L144  | R96           | <b>∟49</b> | RI    | i-46         | R-94  | P~(44  | Q-192 | CRCC |

| 164               | L192  | ₹144          | L97        | 749   | LZ           | R-46  | P-96   | 044   | CRCC |

| 180               | L240  | R192          | L 145      | R97   | L50          | R2    | P- 48  | 0-96  | CRCC |

| 96                | L 288 | R2 <b>4</b> 0 | _193       | R145  | L9 <b>8</b>  | R50   | PO     | 2-48  | CRCC |

| 112               | L336  | R288          | .241       | R193  | JI46         | R98   | 248    | 00    | CRCC |

Wenn die Daten im Bereich von  $\rm H_0$  –  $\rm H_{63}$  ausfallen, bleiben, bedingt durch die Verzögerung, in unserem Beispiel die Daten  $\rm L_2$  und  $\rm R_2$  erhalten, sie erscheinen erst in  $\rm H_{64}$  und  $\rm H_{80}$ .

Nach diesem Prinzip ist sichergestellt, daß von 3 Daten bei einem Drop-out mindestens eine Date erhalten bleibt.

Die Verzögerung beim CD-System beträgt 28 Wörter!

Das Cross-Interleave-System ist eine Kombination von Cross-Code und Interleaving.

Bei der Fehlerkorrektur nach dem CIRC-System arbeitet man zusätzlich noch mit der Bildung von Polynomen, Multiplikationen und Subtraktionen.

- 44 -

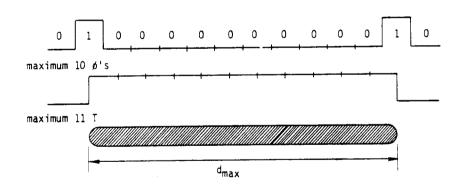

#### CIRC-Verschlüsselung

Die Verschlüsselung nach dem CIRC findet beim CD-Aufzeichnungsprozeß statt.

Das analoge Audiosignal wird in den A/D-Wandlern digitalisiert und steht als Wörter å 16 Bit hinter den Wandlern zur Verfügung.

6 Wörter å 16 Bit des linken Kanals und 6 Wörter å 16 Bit des rechten Kanals werden umgewandelt in 24 Wörter å 8 Bit. Diese 24 Wörter bilden das Eingangssignal für den C2-Codierer. Man bezeichnet sie als Daten-Wörter. Der C2-Codierer hat die Aufgabe diesen 24 Wörtern noch 4 sogenannte "Q-Wörter" å 8 Bit hinzuzufügen.

Es gehen also 24 Wörter å 8 Bit in den C2-Codierer, am Ausgang erhält man 28 Wörter å 8 Bit. Diesen Codierer bezeichnet man deshalb auch als "24/28-Codierer".

Der "C1-Codierer" erhält als Eingangssignal diese 28 Wörter å 8 Bit und fügt 4 sogenannte "P-Wörter" å 8 Bit hinzu. Am Ausgang ergeben sich 32 Wörter å 8 Bit. Daher wird der "C1-Codierer" auch als "28/32-Codierer" bezeichnet.

Nach Abschluß der CIR-Codierung erhält man für jeden Block von 24 Wörtern å 8 Bit am Eingang 32 Wörter å 8 Bit am Ausgang. Diese zusätzlichen 8 Wörter werden als "Redundanzwörter" bezeichnet, sie dienen zur Fehlerkorrektur.

Die Abbildung auf der linken Seite zeigt eine Darstellung der CIRC-Verarbeitung.

## Das Kontroll-Signal

Ein Kontroll-Wort besteht aus 8 Bit und wird im MPX-2-Block der bisherigen Rahmenstruktur (Frame) bestehend aus 24 Daten-Wörtern, 4 P- und 4 Q-Wörtern, hinzugefügt.

Jedes Bit des Kontroll-Wortes kann als Subcode benutzt werden.

Pro Kontrollwort stehen also 8 Kanäle (= 8 Bit), die zu Kennungszwecken genutzt werden können, zur Verfügung. Sie werden alphabetisch von P-W bezeichnet.

Die Kanäle P und Q des Kontrollwortes sind **nicht** mit den Redundant-Wörtern P und Q zu verwechseln.

Der P-Kanal kündigt den Start des Musikstückes an und wird deshalb auch als "Kennzeichenbit" (Flag-Bit) bezeichnet.

Die Kanäle R-W können z.B. als Display-Kanäle verwendet werden, hierfür sind z.Zt. jedoch noch keine Spezifikationen festgelegt.

Beim CDP-101 wird nur der Q-Kanal ausgewertet.

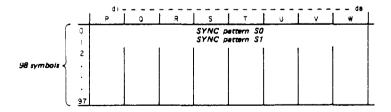

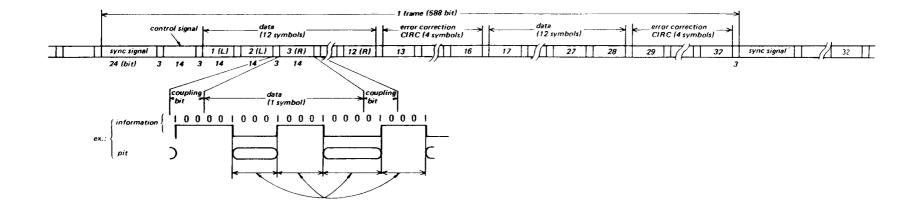

#### Der Steuersignal-Block

Ein Steuersignal-Block besteht aus 98 Wörtern, wie in nachfolgender Abbildung gezeigt.

#### Kanal @

Wenn innerhalb eines Steuersignal-Blocks nur der Kanal Q formuliert ist, so enthält dieser Block auf 98 Wörtern nur einen Q-Kanal mit 98 Bits.

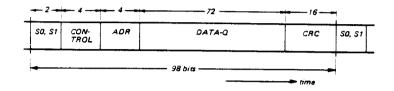

In folgender Abbildung wird die Struktur des Q-Kanals dargestellt.

Erklärung zu obiger Abbildung:

SO, S1

: Synchr. Bits

control

: Zeigt die Anzahl der Übertragungskanäle und die Preemphasis-Funktion an.

0000 - 2-kanalig, keine Preemphasis 1000 - 4-kanalig, keine Preemphasis 0001 - 2-kanalig, mit Preemphasis

1001 - 4-kanalig, mit Preemphasis

LSB = 0 an den "lead in"- und "lead out" -Punkten

ADR

: Kontrollbit für Data Q (ausgehend vom MSB)

Data Q

: 72 Daten-Bits (ausgehend vom MSB)

CRC

: CRC-Korrekturcode bestehend aus Control-, ADR und

Data-Q-Bits (ausgehend vom MSB)

## Der CRC-Code

Mit dem CRC-Code (16 Bit innerhalb des Q-Kanals) kann man Fehler lokalisieren und aus den noch vorhandenen Daten korrigieren. Daher sind in dem CRC-Code Anteile der Control-, ADR- und Data-Q-Information enthalten. Der Cyclic-Redundancy-Check-Code ist einer der meistverwendeten Fehlerlokalisierungs- (und Korrektur-) Codes.

Zur Zeit sind für Kanal Q drei Betriebsarten definiert. Die Differenzierung der Betriebsarten erfolgt durch die Kontrolle der ADR-Bits durch den Prozessor.

Beim CDP-101 erfolgt die Datenverarbeitung nur für die Betriebsart ADR-0001.

## Betriebsart ADR-0001 für Kanal Q

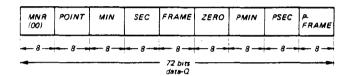

Bei der Betriebsart 1 liegen mindestens 9 oder 10 fortlaufende Subcode-Blöcke am Ausgang. Die Betriebsart 1 wird unterteilt in 2 Datenblöcke, wie sie in nachfolgender Abbildung gezeigt wird.

Datenform in der Einlaufspur (lead in). TOC (table of contents) wird angekündigt.

| MNR | × | MIN | SEC | FRAME     | ZERO | AMIN | ASEC | A-<br>FRAME |

|-----|---|-----|-----|-----------|------|------|------|-------------|

| 8   | 8 | 8   | 8   | - 72 bits | 8    | - 8  | 8-   | 8-          |

Datenform während des Musiksignals und während des Auslaufes (leac out).

Erklärungen zu obiger Abbildung:

MNR: Die Nummer des Musikstückes wird angegeben (2 Ziffern, BCD). 00 lead in, 01-99 Titel-Nr., AA lead out track (Codierung außerhalb des BCD-Codes) Beachten Sie: Während einer Musikanwahl ist MNR = 01-99 jedoch nie 00. Die Zahlenwerte erhöhen sich jeweils um 1 ausgehend von 01!

X: Dem MNR-Index sind die hier vorgegebenen Teilungsraten zugeordnet. Die Teilungsrate ist abhängig von der Software (2 Ziffern, BCD). In der Einlaufspur existiert die "X-Kennung" nicht. 00 Pausen-Kennung (Mutingfunktion). Vor Beginn eines Musikstückes ist jeweils eine Pause von 2-3 Sek. codiert. 01-99 Subcode-Teilungsrate, im Auslauf (lead out) ist X = 01.

Zero: Diese Bits sind alle low.

FRAME, SEC, MIN: Die Spielzeit- und Titelkennung wird auf 3x2 Ziffern\* dargestellt (Codierung auf der Platte BCD). Zu Beginn des Inhalts (Platten-anfang) sind alle Kennungen "O". Die Zeitanzeige erhöht sich während des Abspielens und er niedrigt sich während einer Pause (negativer Zeitvorlauf). Am Ende einer Pause zwischen 2 Titeln ist die Zeitkennung wieder OO. Die Zeit erhöht sich auf der Ein- und Auslaufspur. 1 MIN = 60 SEC., 1 SEC = 75 Frames (=Datenblock)

A FRAME, A SEC, A MIN : Die Abspielinformationen werden (wie oben schon erwähnt) auf 3x2 Ziffern dargestellt (Codierung: BCD). Am Anfang des Platteninhalts ist die Zeitanzeige "O". Der MNR-Code indiziert eine 1. 1 A MIN = 60 A SEC, 1 A SEC = 75 A FRAME (00-74)

**P FRAME, P SEC, P MIN, POINT**: In diesem Abschnitt des Einlaufs (lead in) ist der Plattenindex integriert. Wie die folgende Tabelle zeigt, wird der Plattenindex kontinuierlich und wiederholt in die Einlaufspur gegeben, zu diesem Zeitpunkt ist MNR = 00. Jede Information wird dreimal wiederholt. Die Kennungen P MIN, P SEC und P FRAME beinhalten den Startzeitpunkt des jeweiligen Titels. Die Abweichungen liegen im Bereich von  $\pm$  1 Sekunde.

\* 1 Ziffer = Zahlendarstellung 0-9 = 4 Bit 2 Ziffern = Zahlendarstellung 00-99 = 8 Bit

| Frame number | POINT | PMIN, PSEC, PFRAME       |

|--------------|-------|--------------------------|

| n            | 0.1   | 00,02,32                 |

| n + 1        | 0 1   | 00,02,32                 |

| n + 2        | 0 1   | 00,02,32                 |

| n +3         | Ú 2   | 10, 15, 12               |

| n + 4        | 0.2   | 10, 15, 12               |

| n + 5        | 0 2   | 10, 15, 12               |

| n + 6        | 0 3   | 16, 28, 63               |

| n + 7        | 0.3   | 16, 28, 63               |

| n +8         | 0.3   | 16, 28, 63               |

| n + 9        | 0 4   |                          |

| n + 10       | 0 4   |                          |

| n + 11       | 0 4   |                          |

| n + 12       | 0.5   |                          |

| n + 13       | 0.5   |                          |

| n + 14       | 0.5   |                          |

| n + 15       | 0 6   | 49, 10, 03               |

| n + 16       | 0 6   | 49, 10, 03               |

| n + 17       | 0.6   | 49, 10, 03               |

| n + 18       | Αŭ    | 01, 00, 00               |

| n + 19       | A 0   | 01,00,00                 |

| n + 20       | A 0   | 01.00,00                 |

| n + 21       | A 1   | 06, 00, 00               |

| n + 22       | Al    | 96, 99, 99               |

| n + 23       | Al    | 06.00.00                 |

| n + 24       | A 2   | 52, 48, 41               |

| n + 25       | A 2   | 52, 48, 41               |

| n + 26       | A 2   | 52, 48, 41               |

| n + 27       | 1.0   | 0 0. 0 2. 3 2   repeated |

| n + 28       | 0.1   | 00,02,32                 |

| •            | •     |                          |

| •            |       | '                        |

| •            |       |                          |

## Die EFM (Eight-to-Fourteen-Modulation)

Folgende Forderungen werden an das CD-System gestellt:

1. Einwandfreies Auslesen von Daten mit hoher Informationsdichte.

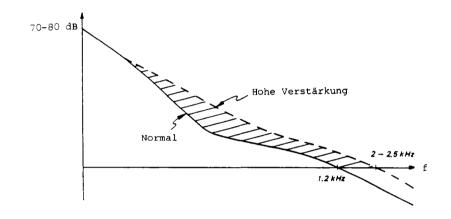

Eine falsche Fokussierung des Laserstrahls oder ein Schrägversatz zur optischen Achse zieht zwangsläufig eine Verschlechterung des Phasen- und Amplitudengangs nach sich.

Das Modulationssystem sollte daher auch bei hoher Informationsdichte gegenüber solchen Abweichungen möglichst unempfindlich sein.

#### 2. Clockinhalt

Die Bitclock ist eines der wichtigsten Signale beim CD-System. Sie dient u.a. zur Synchronisierung der digitalen Daten und zur Servosteuerung. Die Bitclock wird aus den Piträndern und somit aus dem ausgelesenen Signal ermittelt.

Daher muß die Modulation eine ausreichende Anzahl von Übergängen aufweisen, was bedeutet, daß der max. Abstand zwischen den Übergängen Pit/Spiegelebene möglichst klein sein soll, ohne Interferenzstörungen zu erzeugen.

#### 3. NF-Komponente

Die Informationsebene wird durch eine 1,2 mm dicke transparente Kunststoffbeschichtung vor Schmutz und Beschädigungen geschützt.

Staub oder Kratzer auf der Oberfläche verändern jedoch die abgetastete Hüllkurve des Signals und erzeugen ein niederfrequentes Signalrauschen im abgetasteten RF-Signal\*. Das Modulationssystem muß so beschaffen sein, daß echte Informationen von Störanteilen zu trennen sind. Niederfrequente Störanteile im RF-Signal führen auch zu Störungen in den Servosystemen.

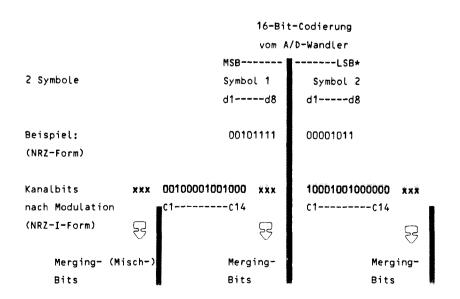

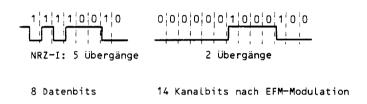

## 4. Fehlerfortpflanzung

Die Neigung des Modulationssystems zur Fehlerfortpflanzung muß möglichst gering sein. Zusätzlich muß es die CIRC-Fehlerkorrektur ermöglichen (jeweils 8 Datenbits pro Wort). Bei der EFM handelt es sich um einen Blockcode, bei dem der sogenannte "Niederfrequenz-anteil" durch Verwendung auszuwählender Mischbits unterdrückt wird. Ein wort bestehend aus 8 Datenbits wird umgewandelt in 14 Kanalbits.

Folgende überlegung steht dahinter:

Ein 8 Bit-Code kann 256 (=2<sup>8</sup>) mögliche Kombinationen darstellen, siehe nachfolgende Abbildung.

\* RF-Signal = HF-Signal

| MSB | 7SB | 6SB | 5SB | 4SB | 3SB | 2SB | LSB | N°  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | o   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 2   |

| -   | -   | -   | -   | -   | -   | -   | -   | -   |

| -   | -   | -   | -   | -   | -   | -   | -   | -   |

| -   | -   | -   | -   | -   | -   | -   | -   | -   |

| 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 254 |

| 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 255 |

Ein 14 Bit-Code ermöglicht jedoch 16384 (=2<sup>14</sup>) Kombinationen, siehe nachfolgende Abbildung.

| MSB | 13SB | 12SB | 11SB | 10SB | 9SB | 8SB | 7SB | 6SB | 5SB | 4SB | 3SB | 2SB | LSB | Ν°    |

|-----|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 0   | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0     |

| 0   | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1     |

| 0   | e    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 2     |

| -   | -    | -    | -    | -    | -   | -   | -   | -   | -   | -   | -   | -   | - ; | -     |

| -   | -    | -    | -    | -    | -   | -   | -   | -   | -   | -   | -   | -   | -   | -     |

| -   | -    | -    | -    | -    | -   | -   | -   | -   | -   | -   | -   | -   | -   | -     |

| 1   | 1    | 1    | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 16382 |

| 1   | 1    | 1    | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 16383 |

Aus diesen 16384 möglichen Kombinationen wählt man nun die aus, in denen mindestens zwei – jedoch weniger als zehn Zero's (0) konstant erscheinen. Nur 267 Kombinationen von 16384 sind geeignet.

Benutzt werden jedoch nur 256 Kombinationen, 11 werden also eliminiert. Anhand einer tabellarischen Auflistung werden den 256 ausgesuchten 14-Bit-Kombinationen in einem ROM 256 8-Bit-Kombinationen zugewiesen.

Ein Beispiel hierfür sehen Sie in nachfolgender Abbildung.

| 8-bit word      |        |     | 14- | -bi | t | wo | oro | i |   |   |   |   |   |   |

|-----------------|--------|-----|-----|-----|---|----|-----|---|---|---|---|---|---|---|

| 0 0 0 0 0 0 1 1 |        | 0 ( | 0 1 | 0   | 0 | 1  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 1 0 0 1 1 1 0 | !      | 0 : | 1 0 | 0   | 0 | 0  | 0   | 1 | 0 | 0 | 1 | 0 | ŋ | 0 |

| 10101010        | i<br>1 | 1 ( | 0 0 | 1   | 0 | 0  | 0   | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 11110010        | 1      | 0 ( | 0 0 | 0   | ð | 0  | 1   | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

Folgende Vorteile ergeben sich hieraus:

- In Verbindung mit dem NRZI-System werden die Anzahl der Übergänge reduziert, somit auch die auf der CD benötigte Bandbreite.

- 2. Die Anzahl der Clock-Elemente erhöht sich (1 x Code a 8 Bit).

- 3. Der NF-Anteil wird reduziert durch Verwendung von sogenannten Mergingbits (Mischbits).

- 4. Die Datenverarbeitung ist einfacher.

- 5. Die Fehlerfortpflanzung ist auf 8 Bit pro 14 Bit beschränkt.

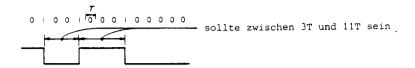

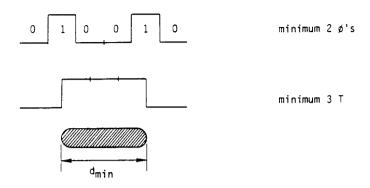

Aus den zuvor aufgestellten Forderungen ergeben sich folgende Spezifikationen für das EFM-System, die sich in der Pit-Anordnung auf der Platte wiederspiegeln. Nach der EFM beträgt der min. Abstand zwischen zwei Übergängen (Pit/Spiegelfläche) 3 Kanalbits (Tmin), der max. Abstand 11 Kanalbits (Tmax).

Wichtig ist auch, daß bei dieser Art der EFM 3 Kanalbits - sie werden als Mergingbits (Mischbits) bezeichnet - für die Verbindung der Wörter untereinander eingefügt werden. Die Mergingbits werden in Überstimmung mit den zuvor erwähnten Forderungen angewendet. Sie enthalten keine Dateninformation. Nachfolgende Abbildung zeigt eine schematische Darstellung des Verarbeitungsablaufes bei der EFM.

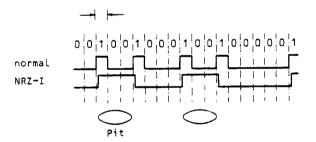

Die folgende Abbildung zeigt den Zusammenhang zwischen den Pits und den 14-BitWörtern unter Berücksichtigung des NRZI-Verfahrens.

Die folgende Abbildung zeigt das Prinzip der Bandbreiten-Verringerung durch Anwendung der EFM in Verbindung mit der NRZI-Methode.

Die folgende Abbildung stellt das Prinzip der NRZI-Methode dar.

## Minimale und maximale Pitlänge

$$T_{min} = 3T$$

, da  $T = -\frac{1}{4\sqrt{3218}}$  us = 231,39 ns

$$d_{min}$$

(bei V = 1,2 m/s) = 3T x  $V_{1,2}$  = 0,833 /um

(bei V = 1,4 m/s) = 3T x  $V_{1,4}$  = 0,972 /um

entspricht auch dem minimalen Abstand zwischen den Pits

$$d_{max}$$

(bei V = 1,2 m/s) = 11T x  $V_{1,2}$  = 3,05 /um

(bei V = 1,4 m/s) = 11 T x  $V_{1,4}$  = 3,56 /um

entspricht auch dem maximalen Abstand zwischen den Pits

- 56 -

# Datenverarbeitung

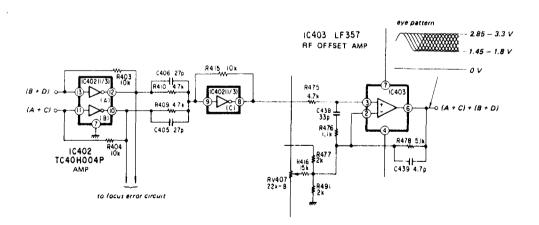

#### HF-Offset-Verstärker

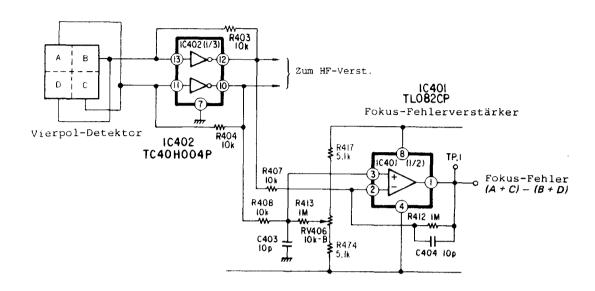

Die Ausgangssignale A+C und D+B des Hauptlichtdetektors werden in IC 402A-B verstärkt und hinter den Ausgängen PIN 10 und 12 addiert, danach führt man das Summensignal (A+B+C+D)) dem Eingang von IC402 PIN 9 zu.

Das nochmals verstärkte Summensignal wird nun an den Eingang des HF-Offset-Verstärkers IC403 gegeben. Hier wird ein fester Gleichspannungspegel von 1,35 V dem HF-Signal unterlegt. Eingestellt wird die Offset-Spannung an RV407.

Die Fokusfehlererkennungsschaltung (focus-error circuit) erhält die Information der Detektorfelder (A+C und B+D) direkt von den Ausgängen PIN 10 und 12 des IC402.

Siehe nachfolgende Abbildung.

Eine Fehljustage des RF-Offset-Pegels (HF-Offset-Pegel) kann dazu führen, daß die Platte nicht angenommen wird. Der RF-Offset-Pegel von 1,35 Volt sollte präzise eingehalten werden.

## Impulsformer-Schaltung

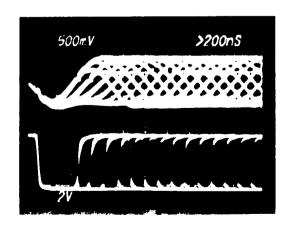

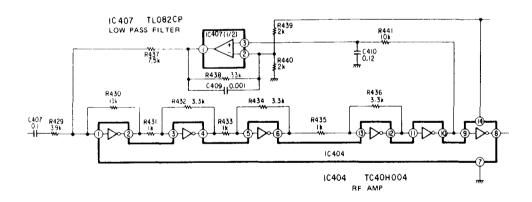

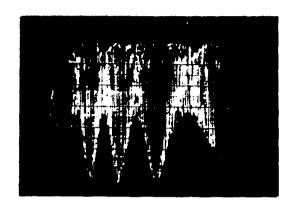

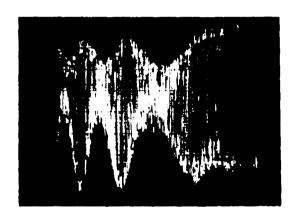

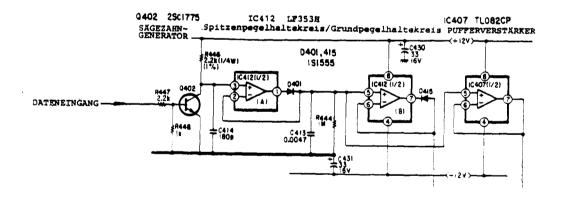

Das von IC403/PIN6 über C407 kommende HF-Signal enthält die von dem Detektor ermittelte Information, es wird an den Eingang PIN1 von IC404 gelegt. Dieses Signal wird als "Eye-Pattern-Signal" bezeichnet. IC404 und IC407 (PIN1, 2, 3) bilden eine Impulsformer-Schaltung.

Sie korrigiert bzw. eliminiert Unregelmäßigkeiten im "Eye-Pattern-Signal", die durch Toleranzen der Plattenoberfläche hervorgerufen werden. IC407 arbeitet in dieser Schaltung als aktives Low-Pass-Filter. Am Ausgang PIN10/IC404 wird das rechteckförmige HF-Signal abgenommen und auf den Eingang der aktiven Low-Pass-Filterschaltung IC407/PIN3 gegeben.

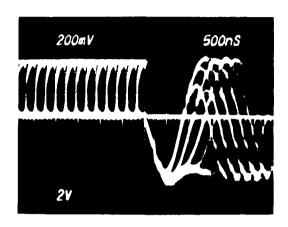

Am Ausgang IC407/PIN1 erhält man durch die Integration eine Gleichspannung, die dem Mittelwert des "Eye-Pattern-Signals" entspricht. Diese Gleichspannung wird dem Eingang PIN1/IC404 zugeführt und dient hier als Vorspannung. Durch diese Maßnahme wird das rechteckförmige HF-Ausgangssignal auf den Mittelwert des Eye-Pattern-Signals "geklemmt".

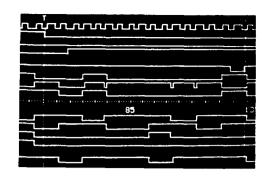

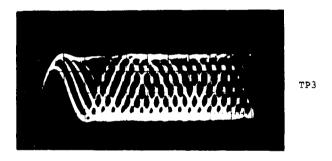

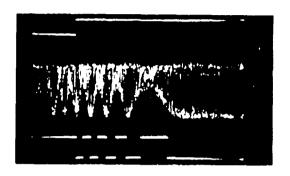

In der Abbildung sehen Sie ein Oszillogramm des Eye-Pattern-Signals, darunter das Ausgangssignal der Impulsformer-Schaltung (PIN8/IC404).

Nachfolgende Abbildung zeigt das Eye-Pattern-Signal mit Mittel-wertachse, auf der das links eingeblendete Ausgangssignal der ImpulsformerSchaltung geklemmt ist. Bedingt durch die Verstärkung des IC404 beträgt das Ausgangssignal ca. 5V<sub>s</sub>, während das "Eye-Pattern-Signal" am Eingang nur ca. 1,2V<sub>ss</sub> aufweist.

Folgende Abbildung zeigt die Impulsformer-Schaltung.

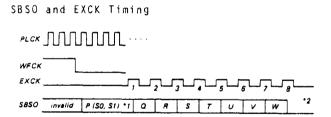

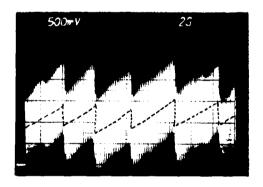

## Wiedergabe-Clock-Frequenz (Pb-clock = PLCK)

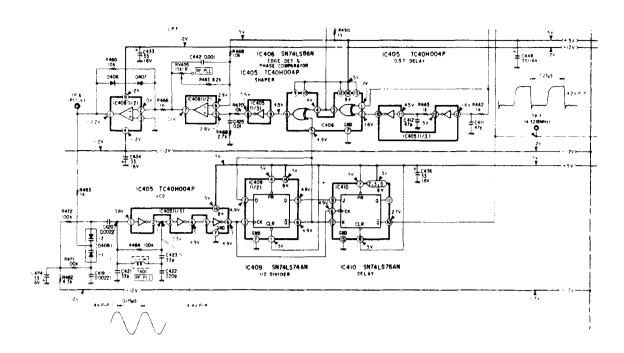

Die von der CD ausgelesene Dateninformation enthält ein 2,16 MHz-Clockelement. Um die Daten einzulesen, benötigt das IC502 (CX7933: EFM-Demodulator und Subcode-Decoder) eine mit der Datenclock synchronisierte Clockfrequenz von 4,32 MHz. Die hierzu benötigte Schaltung wird in nachfolgender Abbildung dargestellt.

Das zuvor besprochene Signal vom Ausgang der Impulsformer-Schaltung (PIN8/IC404) wird an PIN13/IC405 angelegt und vom Ausgang PIN10/IC405 mit einer Verzögerung von  $0.5T = \frac{231.385}{2}$  ns = 115,6925 ns. (T ergibt sich aus der Datenstruktur der CD) and den Eingang PIN2/ IC406 angelegt.

Der Eingang PIN1/IC406 wird mit dem unverzögerten Signal der Impulsformer-Schaltung versorgt. Da die Eingänge PIN1 und 2/IC406 zu einem EX-OR-Gatter gehören, wird die Impulsdauer am Ausgang PIN3/IC406 ebenfalls nur 0,5T = 115,6925 ns betragen. Dieser Impuls liegt am Eingang eines weiteren EX-OR-Gatters (PIN4/IC406).

IC405 bildet mit einer externen Beschaltung einer spannungsgesteuerten Oszillator, er schwingt auf einer Frequenz von 8,64 MHz, das nachgeschaltete IC409 arbeitet als 1/2-Teiler, von seinem Ausgang PIN6 nimmt man Rechteck-Impulse (f = 4,32 MHz) ab und führt sie dem zweiten Eingang des EX-OR-Gatters PIN5/IC406 zu. Es arbeitet als Phasenvergleicher. Bei Phasenungleichheit erhält man am Ausgang PIN6/IC406 Impulse, deren Breite im direkten Zusammenhang mit der Phasendifferenz stehen.

IC405 arbeitet als Impulsformer (shaper) und in IC408, das als aktives Low-Passfilter arbeitet, wird durch Integration eine Nachregelspannung zur Ansteuerung der Kapazitätsdioden des VCO gewonnen. Auf diese Weise erhält man eine Clockfrequenz, die phasenstarr mit der auf der CD gespeicherten Datenclock gekoppelt ist. In IC410 wird die so gewonnene Pb-Clockfrequenz um 90° in der Phasenlage verzögert und dann erst für den EFM-Demodulator (IC502) verwendet.

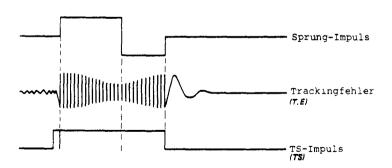

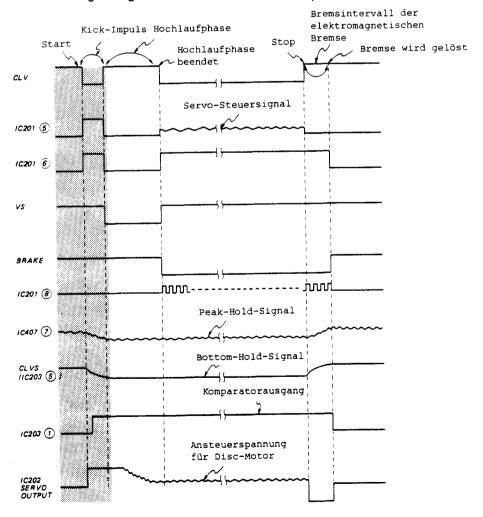

Beachten Sie bitte: Jeweils zu Beginn und am Ende eines Datenblocks (Frame) auf der CD erscheint am Ausgang des EX-OR-Gatters IC406/PIN3 ein 0,5T breiter Impuls!